Texas Instruments 4Q 2006 Interface Selection Guide

x1 PCI Express

®

to 1394a OHCI Bridge

XIO2200A

Get samples, datasheets, EVMs and app reports at:

w

ww.ti.com/sc/device/XIO2200A

Key Features

• x1 PCI Express Primary Interface

• Supports two 1394a ports

• Fully-Compliant with 1394 Open Host Controller Interface

Specification, Revision 1.1

• ExpressCard Reference Design supports two 1394a ports

• Internal dedicated PCI bus operates at 32-bit, 66 MHz

• Compact Footprint, 176-Ball, GGW MicroStar™ BGA or Lead-Free

176-Ball, ZGW MicroStar BGA

Key Benefits

• One-chip solution for 1394a ExpressCards

• Advanced power management features

• Software-programmable and hardware-autonomous power

management

• Supports low-power applications such as ExpressCard

• Compact footprint, 176-ball MicroStar BGA

• EEPROM configuration allows a global unique ID for the 1394

fabric to load

Target Market

• ExpressCards

• PC Add-In Cards

• PC Motherboards

4-Lane, 4-Port PCI Express Switch

XIO3130

www.ti.com/sc/pcl-e *

Expected release 1Q 2007

TI’s XIO3130 is an integrated PCI Express fan-out switch solution

with one upstream x1 port and three downstream x1 ports. This high-

performance, integrated solution provides the latest in PCI Express

switch technology. It features cut-through architecture and integrated

reference clock buffers for downstream ports. The XIO3130 is fully-

compliant with the PCI Express Base Specification Rev. 1.1. It supports

Advanced Error Reporting as defined in the PCI Express base specifica-

tions and is backwards-compatible with the PCI Local Bus

Specification, Rev. 2.3.

Key Features

• PCI Express fan-out switch with x1 upstream port and three x1

downstream ports

• Fully compliant with PCI Express Base Specification, Rev. 1.1

• Cut-through architecture

• Built-in Adaptive Equalizer in each of the four ports

• Wake-event and Beacon support

• Support for D1, D2, D3hot, and D3cold

• Active State Power Management (ASPM)

• Uses both L0s and L1

• Low power PCI Express transmitter mode (pre-emphasis disabled)

• Integrated AUX Power Switch drains VAUX power only when main

power is “off”

• Integrated Hot-Plug Support

• Integrated REFCLK Buffers for Switch Downstream Ports

• Advanced Error Reporting to assist with System Debug Tools

• 3.3V Multifunction I/O pins (e.g. for Hot-Plug status-and-control, or

General Purpose I/Os)

• Listed in PCI-SIG Compliance List

Target Market

The primary purpose of the XIO3130 as a fan-out device is efficiently

expanding the chipset’s computing resources to multiple I/O ports and

enhancing system functionality and flexibility. Target applications for the

XIO3130 include PCs, servers, storage, industrial control and backplane.

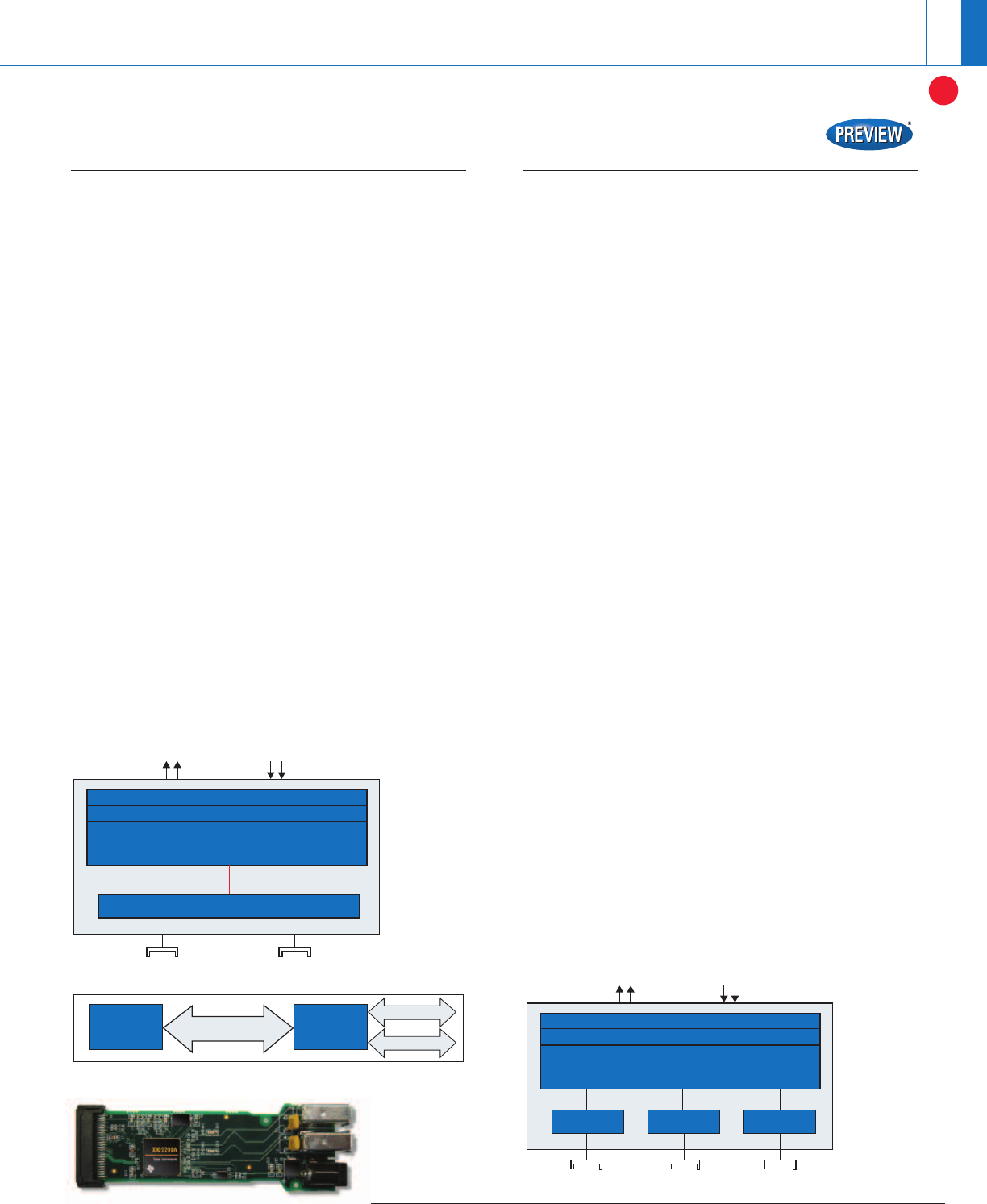

2.5Gbps XMT 2.5Gbps

Internal PCI Bus

PHY Port 0 PHY Port

PCI to 1394a Core

x1 PCI Express Upstream PHY Interface

Digital Link Layer

Transaction Layer:

PCI Bridge Core (32 Bit, 66 MHz)

2.5Gbps 2.5Gbps

PHY Port 0 PHY Port 1

PHY Port 2

Port Logic Port Logic Port Logic

x1 PCI Express Upstream PHY Interface

Digital Link Layer

Transaction Layer:

Crossbar Switch & Packet Control

ExpressCard reference design.

x1 PCI Express 2.5 Gbps

1394a

1394a

South Bridge XIO2200A

PCI Express

®

31

➔