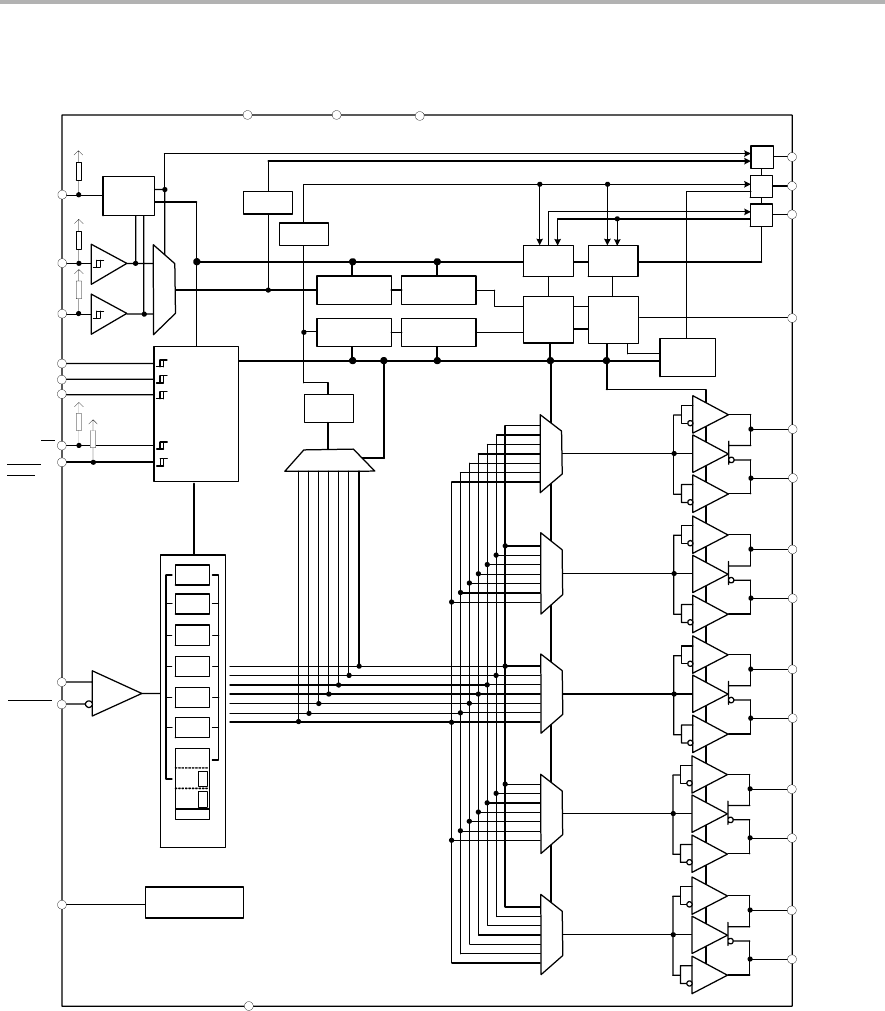

CDCM7005 Functional Block Diagram

1-2

1.1 CDCM7005 Functional Block Diagram

PECL

to

LVCMOS

Progr. Delay

N

PECL

INPUT

CTRL_LE

CTRL_DATA

CTRL_CLK

VCXO_IN

CP_OUT

PLL_LOCK

STATUS_REF /

PRI_SEC_CLK

Bias Generator

VBB

VCC_CP

VCC

AVCC

GND

PRI_REF

SEC_REF

REF_SEL

REF_MUX

LVCMOS

FB_MUX

LV

CMOS

Y0B

Y0A

LV

CMOS

LV

PECL

LV

CMOS

Y1B

Y1A

LV

CMOS

LV

PECL

LV

CMOS

Y2B

Y2A

LV

CMOS

LV

PECL

LV

CMOS

Y3B

Y3A

LV

CMOS

LV

PECL

LV

CMOS

Y4B

Y4A

LV

CMOS

LV

PECL

SPI LOGIC

Manual &

Automatic

CLK Select

Current

Reference

Reference

Clock

freq. detect

> 2 MHz

Selected REF Signal

Progr. Divider

N 2

12

Y0_MUX

P Divider

÷ 3

÷ 4

÷ 6

/8

÷ 8

÷ 16

÷ 1

÷ 2

÷ 4

÷ 8

90

o

90

o

LOCK

Charge

Pump

PFD

HOLD

Y1_MUXY2_MUXY3_MUXY4_MUX

P16−Div

freq. detect

> 2 MHz

Progr. Delay

M

Progr. Divider

M 2

10

Feedback

Clock

V

CC

− 1.3 V

STATUS_VCXO

/ I_REF_CP

VCXO_IN

RESET or

HOLD

PD