Global Reset Only Bits/PME Context Bits

A-2

A.1 Global Reset Only Bits/PME Context Bits

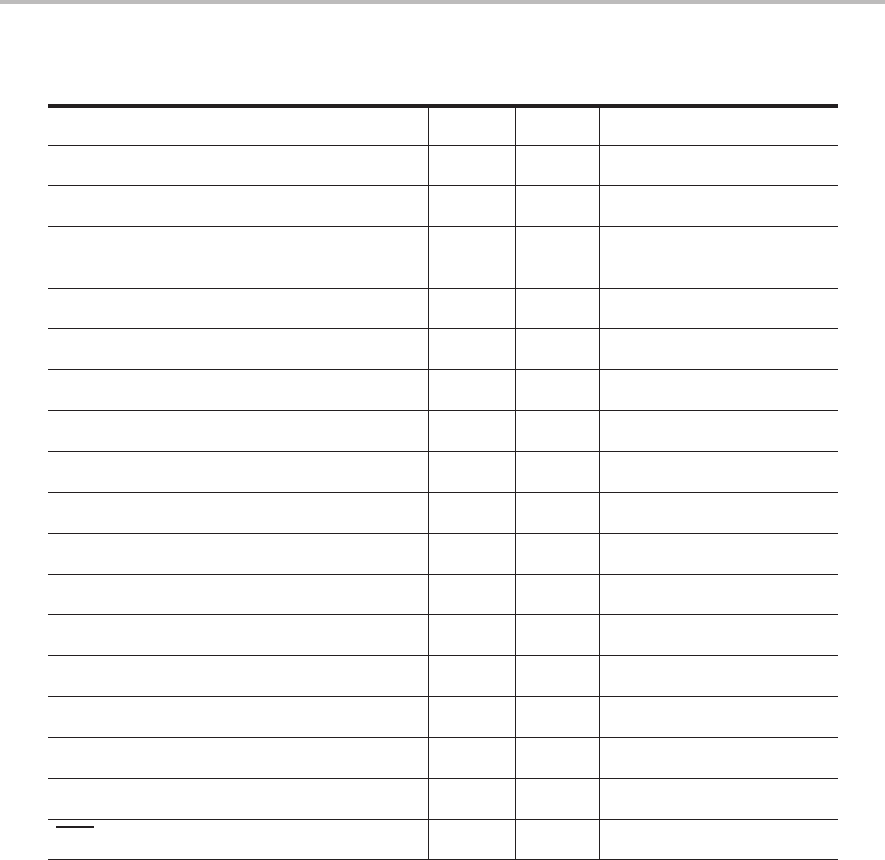

Table A–1.Global Reset Only Cleared Bits

Register Name Space Offset Bit

Subsystem IDs PCI 40h 31–0

PC card 16-bit legacy mode base address PCI 44h 31–1

System control PCI 80h 31–29, 27–24, 22–14, 6–3,

1–0

Multimedia control

PCI

84h 7–0

General status

PCI

85h 2–0

GPIO0 control

PCI

88h 7, 6, 4, 3, 1, 0

GPIO1 control

PCI

89h 7, 6, 3, 1, 0

GPIO2 control

PCI

8Ah 7, 6, 4, 3, 1, 0

GPIO3 control

PCI

8Bh 7, 6, 3, 1, 0

MFUNC routing

PCI

8Ch 31–0

Retry status

PCI

90h 7–1

Card control

PCI

91h 7, 6, 2, 1, 0

Device control

PCI

92h 7–0

Diagnostic

PCI

93h 7–0

Socket DMA register 0

PCI

94h 1–0

Socket DMA register 1

PCI

98h 15–0

GPE control/status

PCI

A8h 10, 9, 8, 2, 1, 0

Note: The following link registers are reset by global reset only.

- PCI subsystem identification register—PCI offset 2Ch

- MIN_GNT and MAX_LAT register—PCI offset 3Eh

- PCI OHCI control register—PCI offset 40h

- Power management control and status register—PCI offset 48h

- PCI miscellaneous and configuration register—PCI offset F0h

- Link enhancement control register—PCI offset F4h

However, there is no support in the OS for the PME-type wake events of the

1394 peripherals at this time.