Chapter 3

AT7/AT7E

3-20

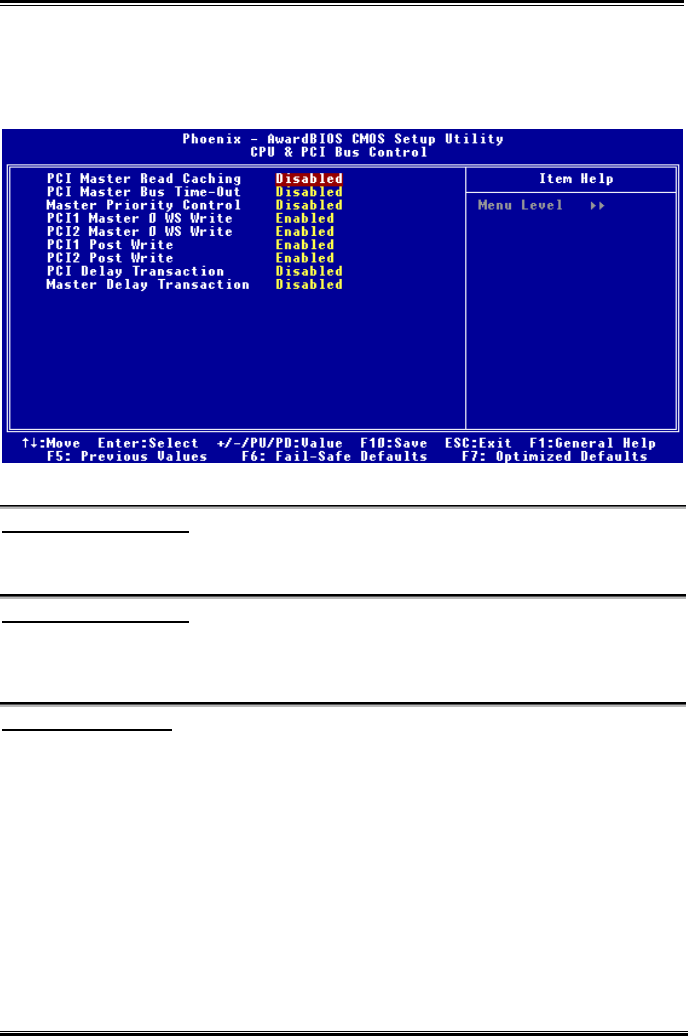

CPU & PCI Bus Control:

This item can let you sets several items concerning the PCI parameters. If you do not understand what

each item does, please keep the default settings as well. Wrong settings will cause system unstablity.

Figure 3-5E. CPU & PCI Bus Control Screen

PCI Master Read Caching:

Two options are available: Disabled or Enabled. The default setting is Disabled. This item can set PCI

bus master read use cache function.

PCI Master Bus Time-Out:

Eight options are available: Disabled ( 001 ( 010 ( 011 ( 100 ( 101 ( 110 (111. The default

setting is Disabled. It can set the time-out period, when after the set time-out period, PCI bus master will

force into arbitration.

Master Priority Control:

Four options are available: Disabled ( 01 ( 10 ( 11. The default setting is Disabled. The full named

of thius item is Master Priority Rotation Control. When setting to “01”, the CPU will always be granted

access after the current bus master completes, no matter how many PCI masters are requesting. With

setting to “10”, if other PCI masters are requesting during the current PCI master grant, the highest

priority master will get the bus after the current master completes. But the CPU will be guaranteed to get

the bus after that master completes. With setting to “11”, if other PCI masters are requesting, the highest

priority will get the bus next, then the next highest priority will get the bus, then the CPU will get the bus.

In other words, with the above settings, even if multiple PCI masters are continuously requesting the bus,

the CPU is guaranteed to get access after every master grant (01), after every other master grant (10) or

after every third master grant (11).