PC 6170 User’s Manual

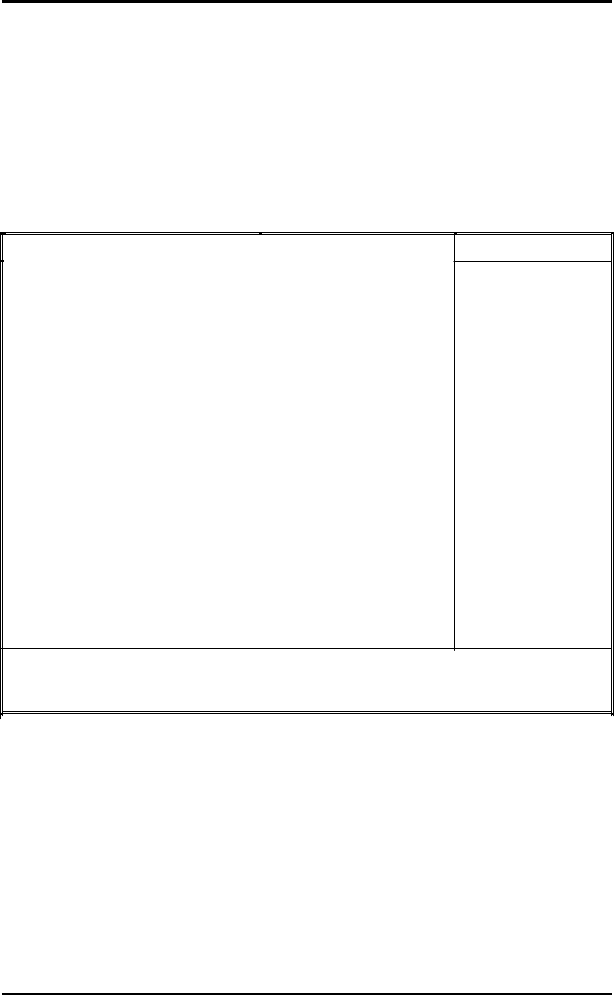

A.3 Advanced Chipset Features

Since

the features in

this section

are related to

the chipset on the

CPU

board and are completely optimized, you are

not

recommended

to change

the

default settings

in this setup table unless you

are

well

oriented with the

chipset

features.

CMOS Setup

Utility-Copyright © 1984-2001

Aw

ard

Softw

are

Ad

vanced Chipset

Featu

res

DRAM

Timing

By

SPD

Ite

m

He

lp

CA

Ss

Latency

Ti

me

2.5

Acti

ve to

Re

charge De

lay

7

Menu

Level

f

D

RAM

RA

S

#

to

CA

S#

De

l

a

y

3

DRAM

RAS#

Re

charge

3

D

RAM

Data

In

te

g

r

ity Mo

de

No

n

-E

CC

MGM Co

re

Fr

eq

uency

Au

to

Max 400/333MHz

System B

IOS

C

acheable

Enable

Video

BIOS

Ca

cheable

Di

sabled

Memory Ho

le At

15

M-16M

Di

sabled

Delayed Transacti

on

Di

sabled

Delay Prior

to Thermal

16

Min

AGP Aperture S

i

ze

(M

B)

64

In

it Di

splay

Fi

rst

Onboard

** On-Chip VGA

Se

tting **

On-Chip VG

A

Enabled

On-Chip Frame Bu

ffe

r Size

32

MB

Boot Displ

ay

Au

to

Pane

l Scaling

Au

to

Panel Number

640 x480

ÇÈ

ÆÅ

:

Mo

ve

E

n

te

r:

S

e

le

ct

+/-

/

P

U

/P

D

:

Va

lu

e

F

1

0

:

S

a

ve

E

S

C

:

E

xi

t

F

1

:

Gene

ral He

lp

F

5

:

P

r

evious

Values F6: Fail-

Saf

e

D

e

f

a

ults F7: O

p

timize

d D

e

f

a

ults

SDRAM

CAS latency Time

You can select CAS latency time in

HCLKs

2, 3, or Auto.

The board

designer should set the values in this field, depending on the DRAM

installed.

Do not change

the

values

in this field unless

you change

specifications of

the

installed

DRAM or the installed CPU.

DRAM Data Integrity Mode

This option sets the data integrity mode of the DRAM installed in the

system.

The default setting

is

“

Non-ECC

”

.

SBC83810 BIOS

Setup

45