Acquiring Data

Touch RUN and the logic analyzer will begin to

acquire data. The analyzer will continue to acquire

data and will display the data when the analyzer

memory is full, the trigger specification is TRUE or

when you touch STOP.

The logic analyzer will flash “Waiting for Trigger” or

“occurrences remaining in level x” where x is number

of the unsatisfied trigger level if the trigger condition is

not satisfied.

POD 3 Description

Pod 3 was included in the USB Analysis Probe to give

the user a detailed look at the USB wire. The USB

Analysis Probe interface contains its own fully

compliant USB serial interface engine (SIE). The

state bits for the USB state machines for this SIE are

available on POD 3. In addition the recovered clock,

recovered data, start of frame, end of packet, end of

sync and low speed/high speed detect signals are

available. These signals are useful for :

• Shadowing the state of the target USB SIE when

that SIE state is unavailable.

• Comparing the state of the target USB SIE with

that of the Analysis Probe SIE.

• Making accurate time measurements of USB

events.

• Accurate USB protocol violation detection.

• Accurate USB signaling violation detection.

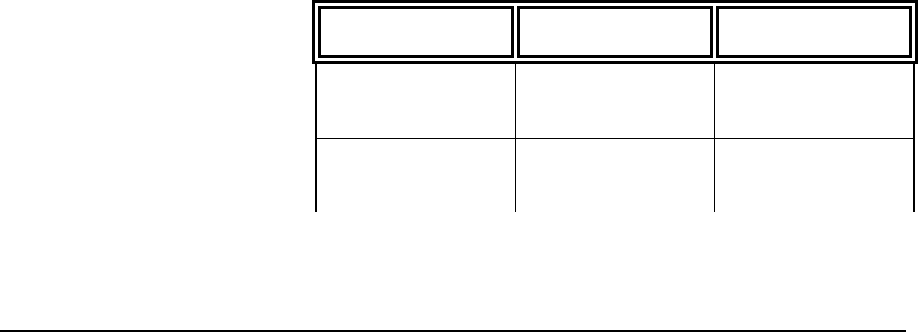

POD 3 channel Signal Name Description

16 CLK12 Recovered

Clock

15 MDATA Recovered

Serial Data

30