ECM-3612

40 ECM-3612 User’s Manual

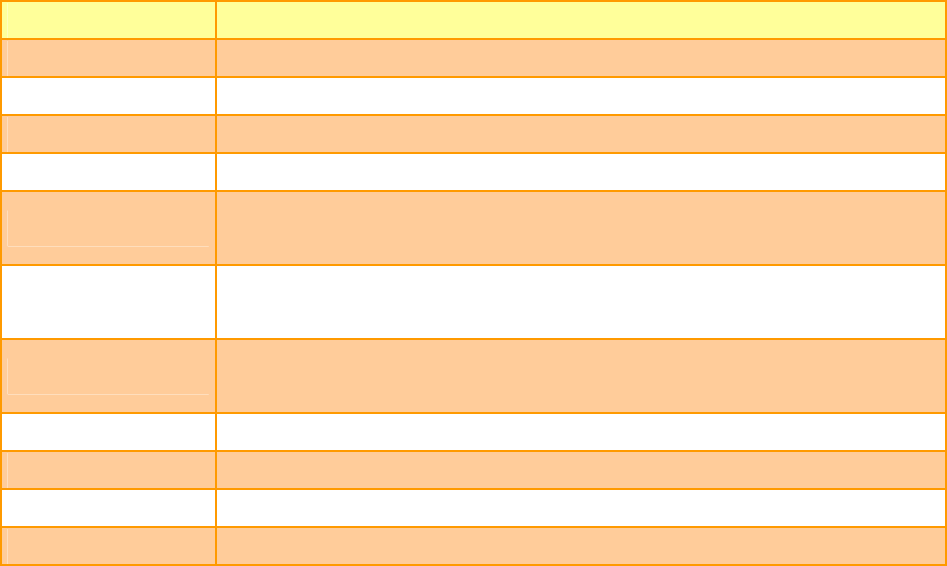

2.3.13.1 Signal Description – Primary & Secondary LCD Panel Connector (CN6, CN8)

Signal Signal Description

P [35:0] Flat Panel Data Bit 35 to Bit 0 for panel implementation.

SHFCLK Shift Clock. Pixel clock for flat panel data

LP Latch Pulse. Flat panel equivalent of HSYNC (horizontal synchronization)

FLM First Line Marker. Flat panel equivalent of VSYNC (vertical synchronization)

M

Multipurpose signal, function depends on panel type. May be used as AC drive

control signal or as BLANK# or Display Enable signal

ENBKL

Enable backlight signal. This signal is controlled as a part of the panel power

sequencing

ENVEE

Enable VEE. Signal to control the panel power-on/off sequencing. A high level

may turn on the VEE (LCD bias voltage) supply to the panel

Y[2:0]P, Z[2:0]P 1

st

& 2

nd

Channel Positive LVDS differentiaI data output

Y[2:0]M, Z[2:0]M 1

st

& 2

nd

Channel Negative LVDS differential data output

YCP, ZCP 1

st

& 2

nd

Channel Positive LVDS differential clock output

YCM, ZCM 1

st

& 2

nd

Channel Negative LVDS differential clock output