User’s Manual

ECM-3612 User’s Manual

45

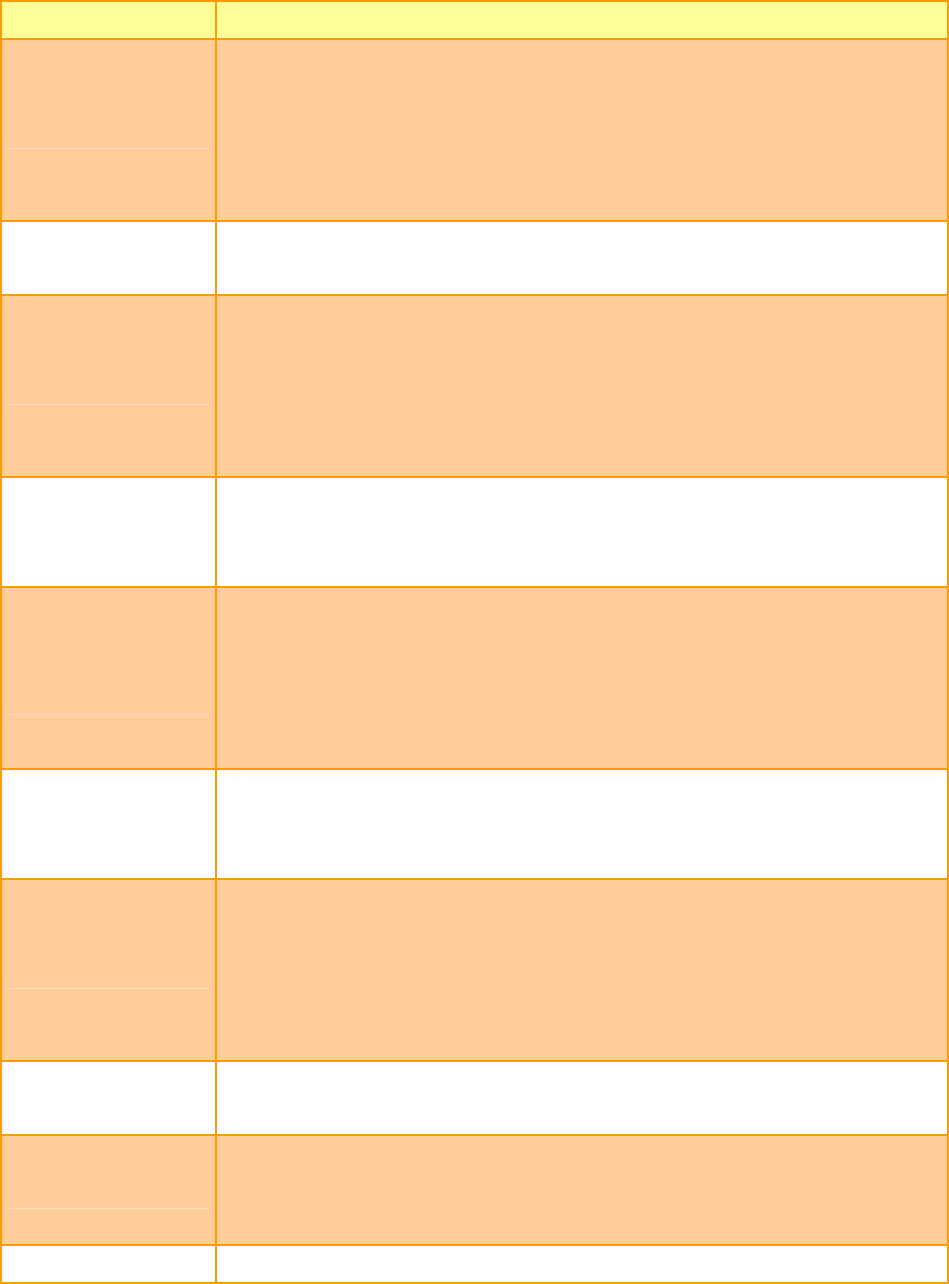

Signal Signal Description

SYSCLK

This clock signal may vary in frequency from 2.5 MHz to 25.0 MHz depending on

the setup made in the BIOS. Frequencies above 16 MHz are not recommended.

The standard states 6 MHz to 8.33 MHz, but most new adapters are able to

handle higher frequencies. The PCAT/PC104 bus timing is based on this clock

signal.

OSC

This is a clock signal with a 14.31818 MHz ± 50 ppm frequency and a 50 ± 5%

duty cycle. The signal is driven by the permanent master.

RESETDRV

This active high signal indicates that the adapter should be brought to an initial

reset condition. This signal will be asserted by the permanent master on the bus

for at least 100 ms at power-up or watchdog time-out to ensure that adapters in

the system are properly reset. When active, all adapters should turn off or tri-state

all drivers connected to the bus.

IRQ[3:7],

IRQ[9:12],

IRQ[14:15]

These signals are active high signals, which indicate the presence of an

interrupting PCAT/PC104 bus adapter. Due to the use of pull-ups, unused

interrupt inputs must be masked.

DRQ[0:3],

DRQ[5:7]

These signals are active high signals driven by a DMA bus adapter to indicate a

request for a DMA bus operation. DRQ [0:3] request 8 bit DMA operations, while

DRQ [5:7] request 16 bit operations. All bus DMA adapters will drive these lines

with a tri-state driver. The permanent master monitors these signals to determine

which of the DMA devices, if any, are requesting the bus.

DACK[0:3]#,

DACK[5:7]#

These signals are active low signals driven by the permanent master to indicate

that a DMA operation can begin. They are continuously driven by a totem pole

driver for DMA channels attached.

AEN

This signal is an active high totem pole signal driven by the permanent master to

indicate that the address lines are driven by the DMA controller. The assertion of

AEN disables response to I/O port addresses when I/O command strobes are

asserted. AEN being asserted, only the device with active DACKn# should

respond.

REFRESH#

This is an active low signal driven by the current master to indicate a memory

refresh operation. The current master will drive this line with a tri-state driver.

TC

This active high signal is asserted during a read or write command indicating that

the DMA controller has reached a terminal count for the current transfer. DACKn#

must be presented by the bus adapter to validate the TC signal.

MASTER# This signal is not supported by the chipset.