User’s Manual

ECM-3612 User’s Manual

43

2.3.15.1 Signal Description – PC/104+ Connecter (CN7, CN10)

Signal Signal Description

LA[23:17]

The address signals LA [23:17] define the selection of a 128KB section of

memory space within the 16MB address range of the 16-bit data bus. These

signals are active high. The validity of the MEMCS16# depends on these signals

only. These address lines are presented to the system with tri-state drivers. The

permanent master drives these lines except when an alternate master cycle

occurs; in this case, the temporary master drives these lines. The LA signals are

not defined for I/O accesses.

SA[19:0]

System address. Address lines for the first one Megabyte of memory. SA [9:0]

used for I/O addresses. SA0 is the least significant bit.

SBHE#

This signal is an active low signal, that indicates that a byte is being transferred

on the upper byte (SD [15:8)) of the 16 bit bus. All bus masters will drive this line

with a tri-state driver.

SD[15:8]

These signals are defined for the high order byte of the 16-bit data bus. Memory

or I/O transfers on this part of the bus are defined when SBHE# is active.

SD[7:0]

These signals are defined for the low order byte of the 16-bit data bus being the

only bus for 8 bit PC-AT/PC104 adapter boards. Memory or I/O transfers on this

part of the data bus are defined for 8-bit operations with even or odd addresses

and for 16-bit operations for odd addresses only. The signals SA0 and SBHE#

are used to define the data present on this bus:

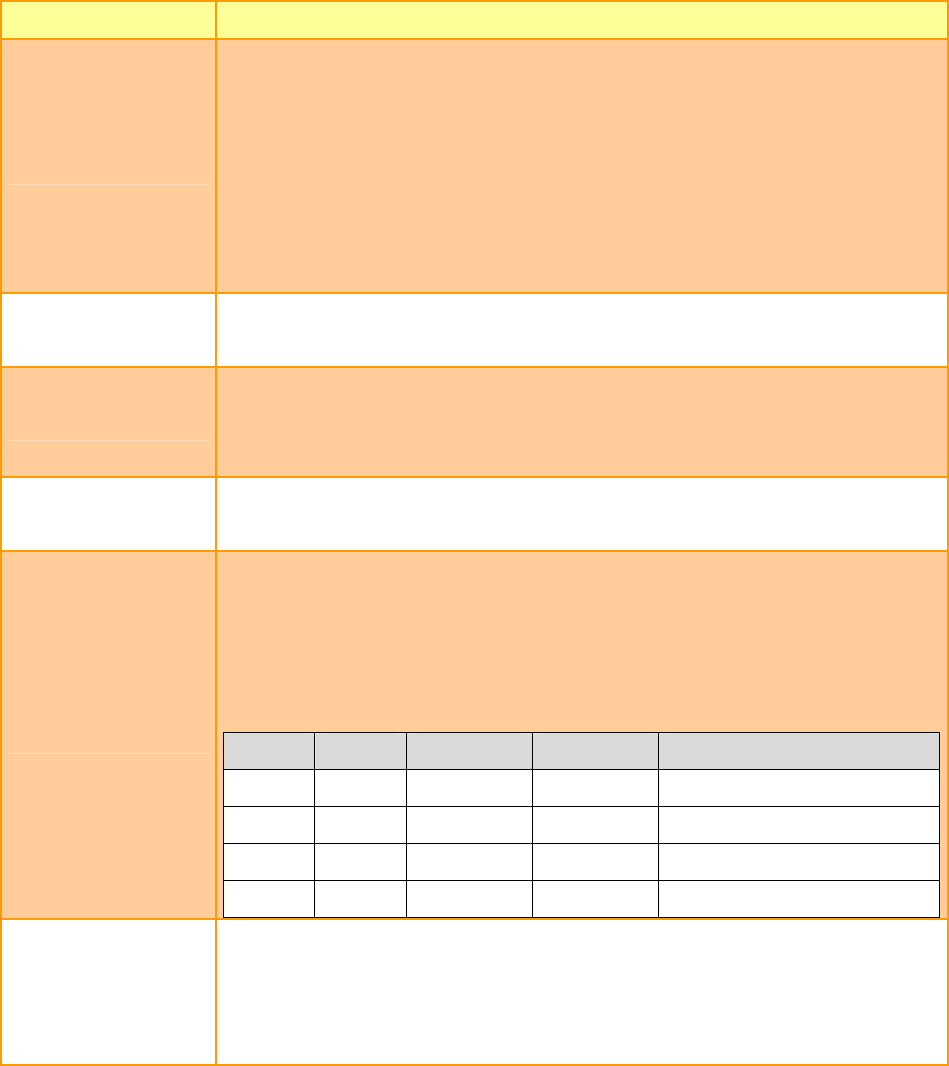

SBHE# SA0 SD15-SD8 SD7-SD0 Action

0 0 ODD EVEN Word transfer

0 1 ODD ODD Byte transfer on SD15-SD8

1 0 - EVEN Byte transfer on SD7-SD0

1 1 - ODD Byte transfer on SD7

BALE

This is an active high signal used to latch valid addresses from the current bus

master on the falling edge of BALE. During DMA, refresh and alternate master

cycles, BALE is forced high for the duration of the transfer. BALE is driven by the

permanent master with a totem-pole driver.