ASUS P3B-1394 User’s Manual52

4. BIOS SETUP

4. BIOS SETUP

Chipset Features

Video Memory Cache Mode (UC)

USWC (uncacheable, speculative write combining) is a new cache technology for

the video memory of the processor. It can greatly improve the display speed by

caching the display data. You must leave this on the default setting of UC

(uncacheable) if your display card cannot support this feature or else your system

may not boot.

PCI 2.1 Support (Enabled)

This function allows you to enable or disable PCI 2.1 features including passive release

and delayed transaction. Leave Enabled (default setting) for PCI 2.1 compliancy.

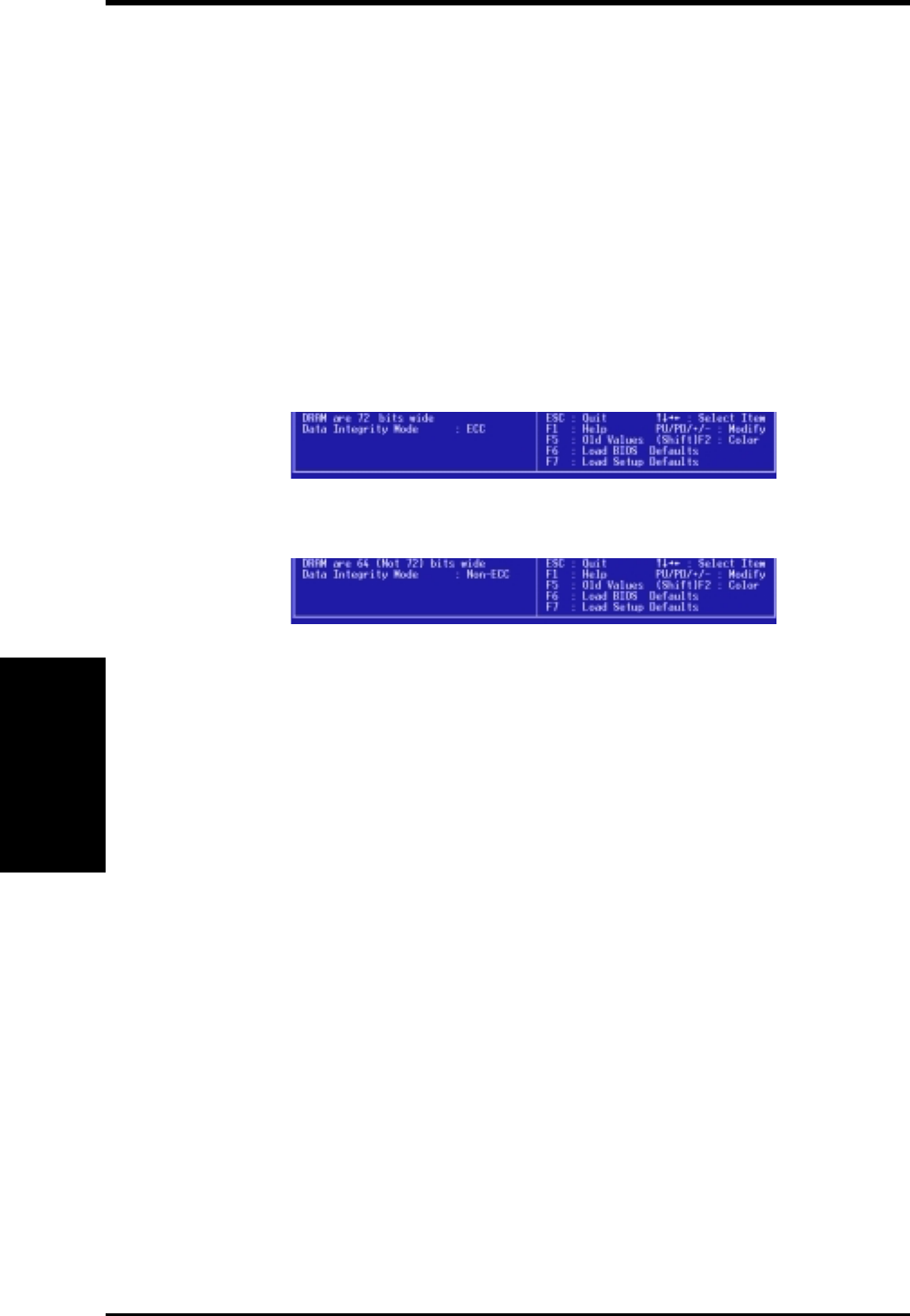

DRAM are xx bits wide

If all your DRAM modules have ECC chips (e.g., 8 chips + 1 ECC chips), they are

considered 72bits and the following will be displayed:

If your DRAM modules do not have ECC chips (e.g. 8 chips), they are considered

64 bits and the following will be displayed instead:

Data Integrity Mode (Non-ECC)

Non-ECC has byte-wise write capability but no provision for protecting data integrity in

the DRAM array. EC-Only data errors are detected but not corrected. ECC with hard-

ware scrubbing allows a detection of single-bit and multiple-bit errors and recovery of

single-bit errors. (See section III for more information on DRAM memory modules.)

....................................................................................................................................

Onboard FDC Controller (Enabled)

When Enabled, this field allows you to connect your floppy disk drives to the

onboard floppy disk drive connector instead of a separate controller card. If you

want to use a different controller card to connect the floppy disk drives, set this

field to Disabled.

Onboard Serial Port 1 (3F8H/IRQ4)

The settings are 3F8H/IRQ4, 2F8H/IRQ3, 3E8H/IRQ4, 2E8H/IRQ10, and Disabled

for the onboard serial connector.

Onboard Serial Port 2 (2F8H/IRQ3)

The settings are 3F8H/IRQ4, 2F8H/IRQ3, 3E8H/IRQ4, 2E8H/IRQ10, and Disabled

for the onboard serial connector.