Appendix

COM-2(PC)F62

C. The Details on NS16550

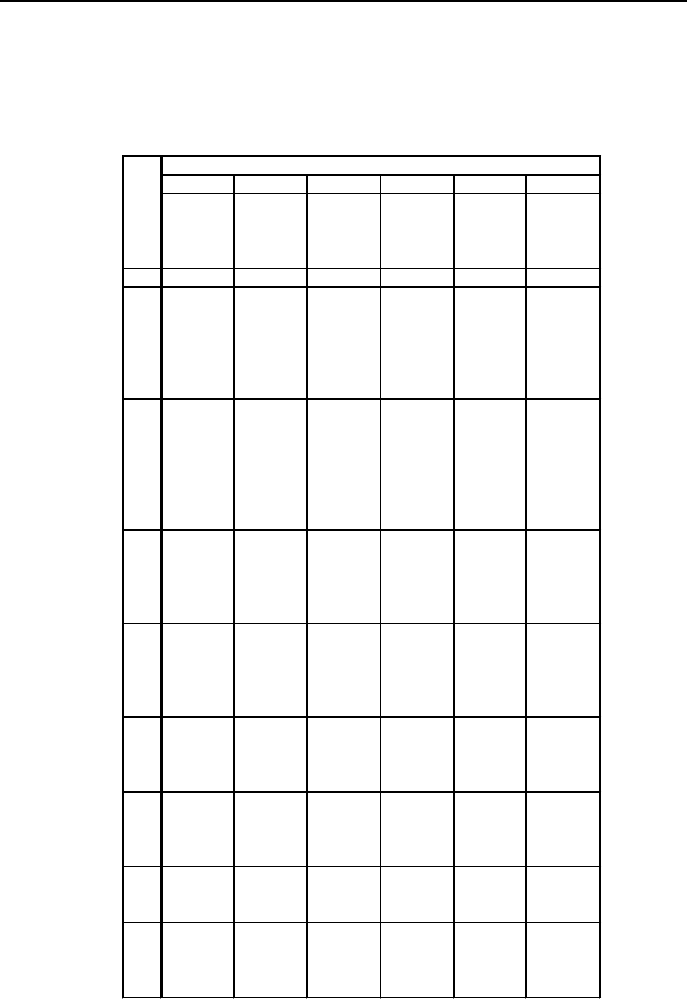

Table 6.9. NS16550's Register

(Short from National Semiconductor's data book)

< 1 / 2 >

Register

0 DLAB = 0 0 DLAB = 0 1 DLAB = 0 2 2 3

Bit Receiver Transmitter Interrupt Interrupt FIFO Line

No. Buffer Holding Enable Ident. Control Control

Register Register Register Register Register Register

(Read Only) (Write Only) (Read Only) (Write Only)

RBR THR IER IIR FCR LCR

0 Data Bit 0 Data Bit 0 Enable "0" if FIFO Word

Received Interrupt Enable Length

Data Pending Select

Available Bit 0

Interrupt (WLS0)

(ERBFI)

1 Data Bit 1 Data Bit 1 Enable Interrupt RCVR Word

Transmitter ID FIFO Length

Holding Bit (0) Reset Select

Register Bit 1

Empty (WLS1)

Interrupt

(ETBEI)

2 Data Bit 2 Data Bit 2 Enable Interrupt XMIT Number of

Receiver ID FIFO Stop Bits

Line Status Bit (1) Reset (STB)

Interrupt

(ELSI)

3 Data Bit 3 Data Bit 3 Enable Interrupt DMA Parity

MODEM ID Mode Enable

Status Bit (2) Select (PEN)

Interrupt

(EDSSI)

4 Data Bit 4 Data Bit 4 0 0 Reserved Even

Parity

Select

(EPS)

5 Data Bit 5 Data Bit 5 0 0 Reserved Stick

Parity

6 Data Bit 6 Data Bit 6 0 FIFOs RCVR Set

Enabled Trigger Break

(LSB)

7 Data Bit 7 Data Bit 7 0 FIFOs RCVR Divisor

Enabled Trigger Latch

(MSB) Access Bit

(DLAB)