CY14B256K

Document Number: 001-06431 Rev. *H Page 21 of 28

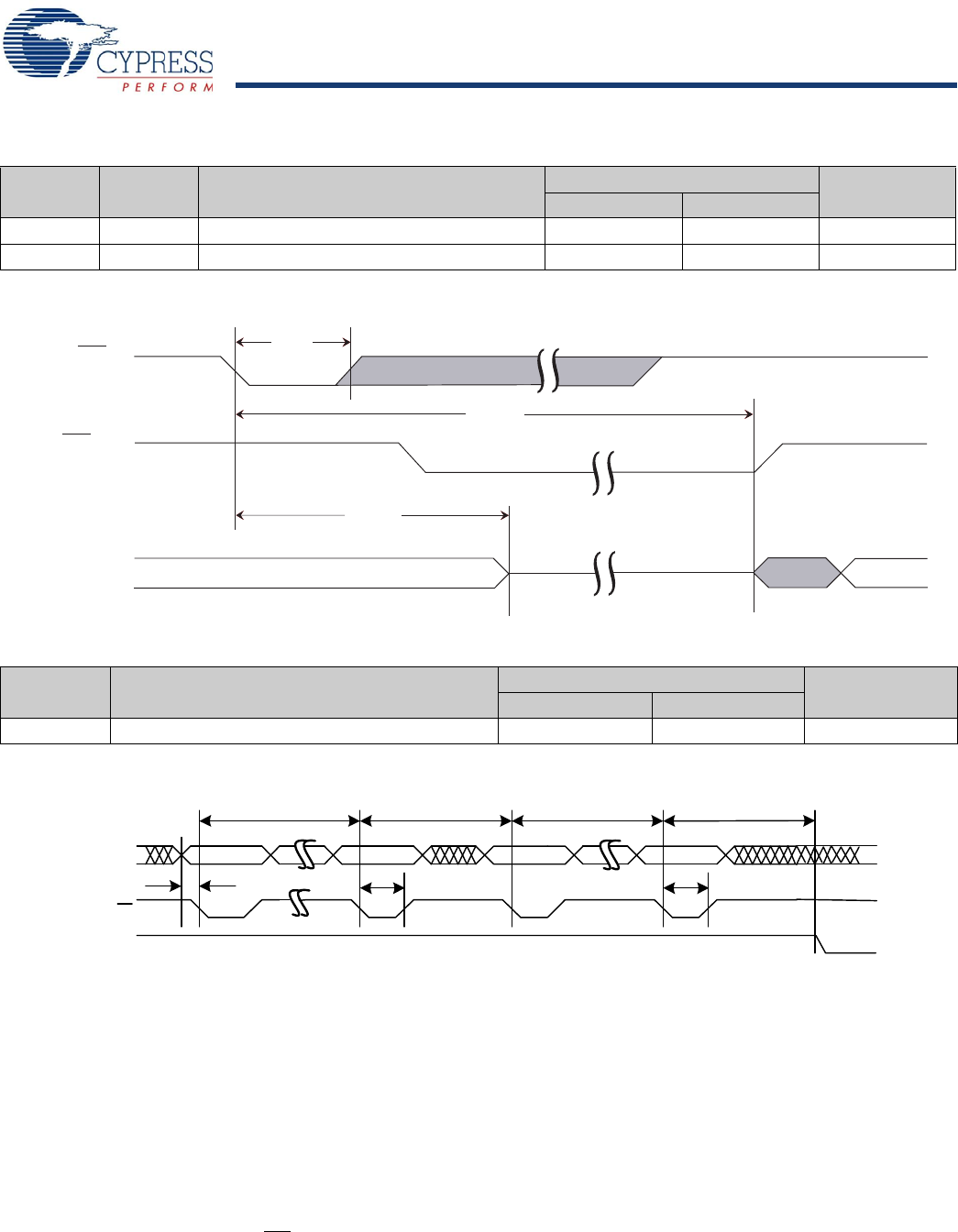

Hardware STORE Cycle

Parameter

Alt.

Parameter

Description

CY14B256K

Unit

Min Max

t

DELAY

[22]

Time Allowed to Complete SRAM Cycle 1 70 μs

t

PHSB

t

HLHX

Hardware STORE Pulse Width 15 ns

Figure 15. Hardware STORE Cycle

Soft Sequence Commands

Parameter Description

CY14B256K

Unit

Min Max

t

SS

[23, 24]

Soft Sequence Processing Time 70 μs

Figure 16. Soft Sequence Processing

[23, 24]

W

+/+;

W

6725(

W

+/%/

W

'(/$<

'$7$9$/,'

'$7$9$/,'

+,*+,03('$1&(

+,*+,03('$1&(

+6%,1

'4'$7$287

+6%287

W

3+6%

$GGUHVV $GGUHVV $GGUHVV $GGUHVV

6RIW6HTXHQFH

&RPPDQG

W

66

W

66

&(

$GGUHVV

9

&&

W

6$

W

&:

6RIW6HTXHQFH

&RPPDQG

W

&:

Notes

22.Read and Write cycles in progress before HSB

are given this amount of time to complete.

23.This is the amount of time it takes to take action on a soft sequence command. Vcc power must remain HIGH to effectively register command.

24.Commands such as STORE and RECALL lock out IO until operation is complete which further increases this time. See specific command.

[+] Feedback