. . . . .

www.digiembedded.com 73

. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .

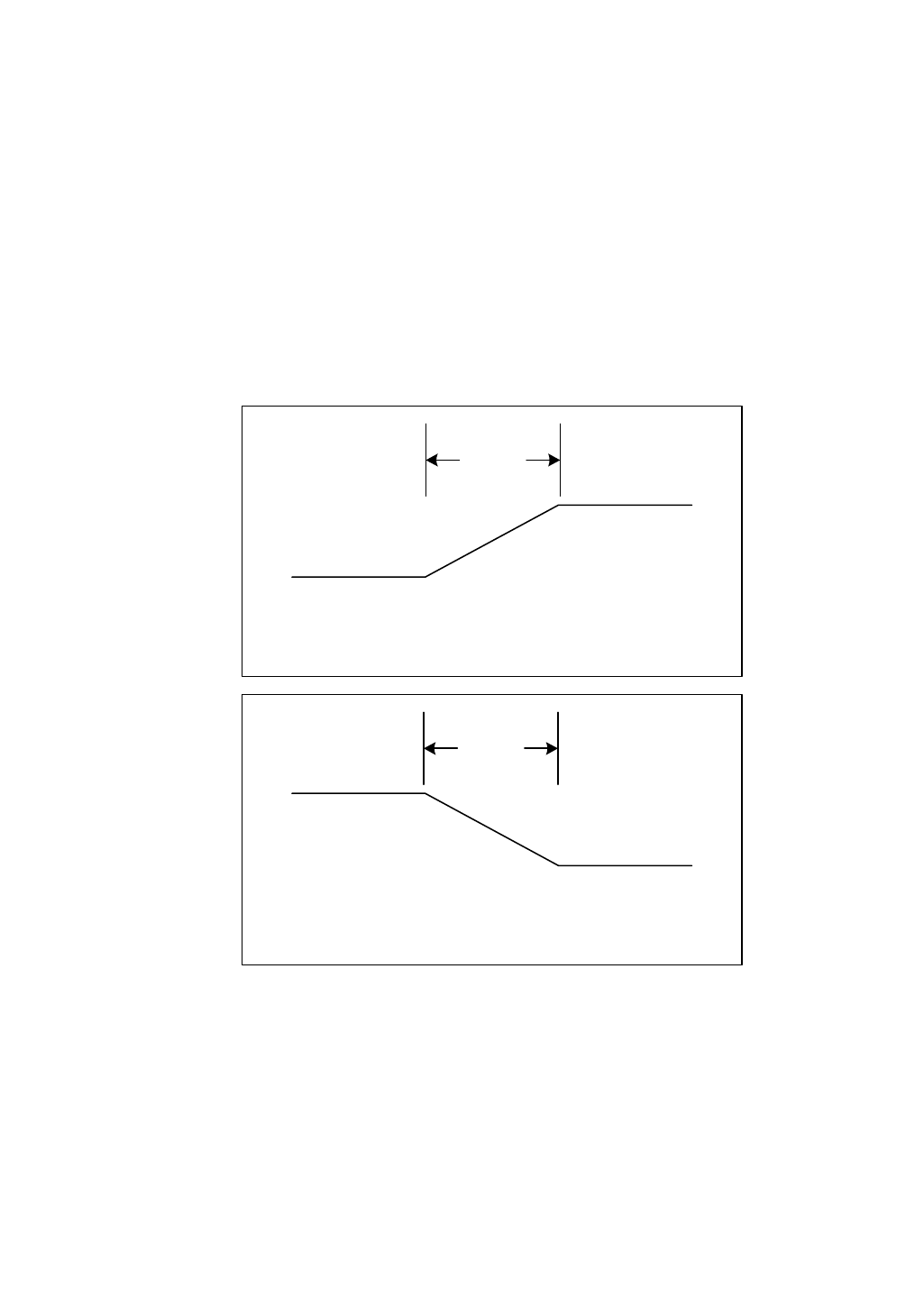

Reset and edge sensitive input timing requirements

The critical timing requirement is the rise and fall time of the input. If the rise time

is too slow for the reset input, the hardware strapping options may be registered

incorrectly. If the rise time of a positive-edge-triggered external interrupt is too

slow, then an interrupt may be detected on both the rising and falling edge of the

input signal.

A maximum rise and fall time must be met to ensure that reset and edge sensitive

inputs are handled correctly. With Digi processors, the maximum is 500 nanoseconds

as shown:

On the NS9210 Processor Module JumpStart there was a measurement of 220ns rise

time and 10ns fall time.

negative edge input

t

F

max = 500nsec

V

IN

= 2.0V to 0.8V

t

F

reset_n or positive edge input

t

R

max = 500nsec

V

IN

= 0.8V to 2.0V

t

R