Source Format:

Operation:

OP-Code:

Type:

Clock Cycles:

Flag:

Description:

Example:

Source Format:

Operation:

OP-Code:

Type:

Clock Cycles:

Flag:

Description:

Example:

MSB LSB

MSB LSB

C –

Z –

D –

I –

C –

Z –

D –

I –

46 EPSON S1C6200/6200A CORE CPU MANUAL

3 INSTRUCTION SET

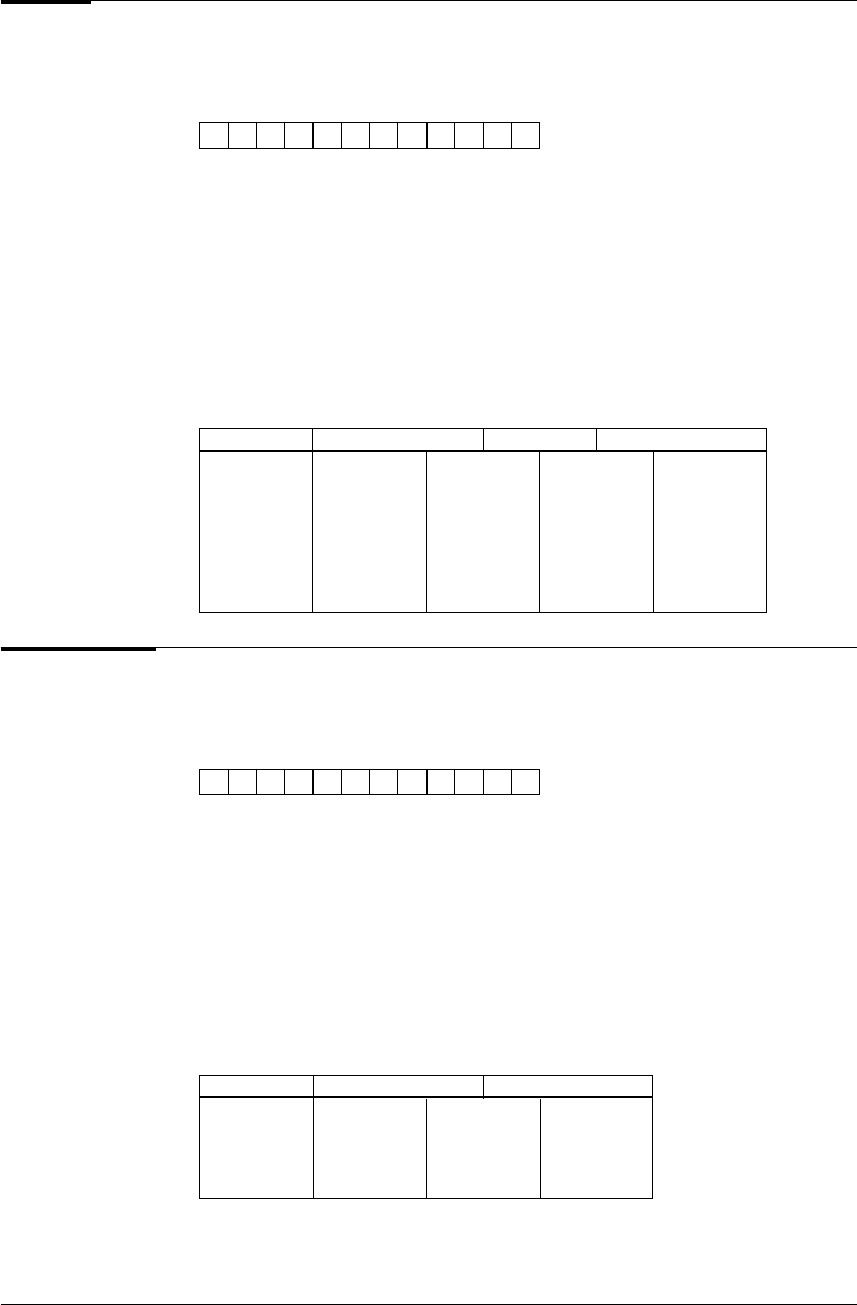

JP Z,s Jump if zero

JP Z,s

PCB ← NBP, PCP ← NPP, PCS ← s

7 to s0 if Z = 1

0110s

7 s6 s5 s4 s3 s2 s1 s0 600H to 6FFH

I

5

Not affected

Not affected

Not affected

Not affected

Jumps to the destination address specified by the 8-bit operand when the zero flag

is set.

SUB A,B PSET 1BH JP Z,10H

PCB 0 0 0 1

NBP 0 0 1 1

PCP 0101 0101 0101 1011

NPP 0001 0001 1011 1011

PCS 0000 0010 0000 0011 0000 0100 0001 0000

A register 0110 0000 0000 0000

B register 0110 0110 0110 0110

Z flag 0 1 1 1

LBPX MX,e Load immediate data e to memory, and increment X by 2

LBPX MX,e

M(X) ← e

3 to e0, M(X+1) ← e7 to e4, X ← X + 2

1001e

7 e6 e5 e4 e3 e2 e1 e0 900H to 9FFH

I

5

Not affected

Not affected

Not affected

Not affected

Stores 8-bit immediate data e in two, consecutive 4-bit locations in data memory.

The X-register is incremented by 2. An overflow in X does not affect the flags.

LBPX MX,18H LBPX MX,36H

X register 0001 1110 0010 0000 0010 0010

Memory (1EH) 0010 1000 1000

Memory (1FH) 1111 0001 0001

Memory (20H) 0000 0000 0110

Memory (21H) 0111 0111 0011