86 EPSON S1C6200/6200A CORE CPU MANUAL

APPENDIX A. S1C6200A (ADVANCED S1C6200) CORE CPU

<Reference 1> Writing on the interrupt mask register during EI

This section describes the operation for writing on the interrupt mask register during EI (enable interrupt

flag) in the regular 1-chip micro controller which uses S1C6200 Core CPU and in the regular 1-chip micro

controller which uses S1C6200A Core CPU. For information on accurate operation, see the respective

hardware manuals of the S1C62 Family.

Table A2.2.2 Writing on the interrupt mask register at EI

Writing on the interrupt mask register at EI

S1C6200

Not possible

S1C6200A

Possible

CPU Core

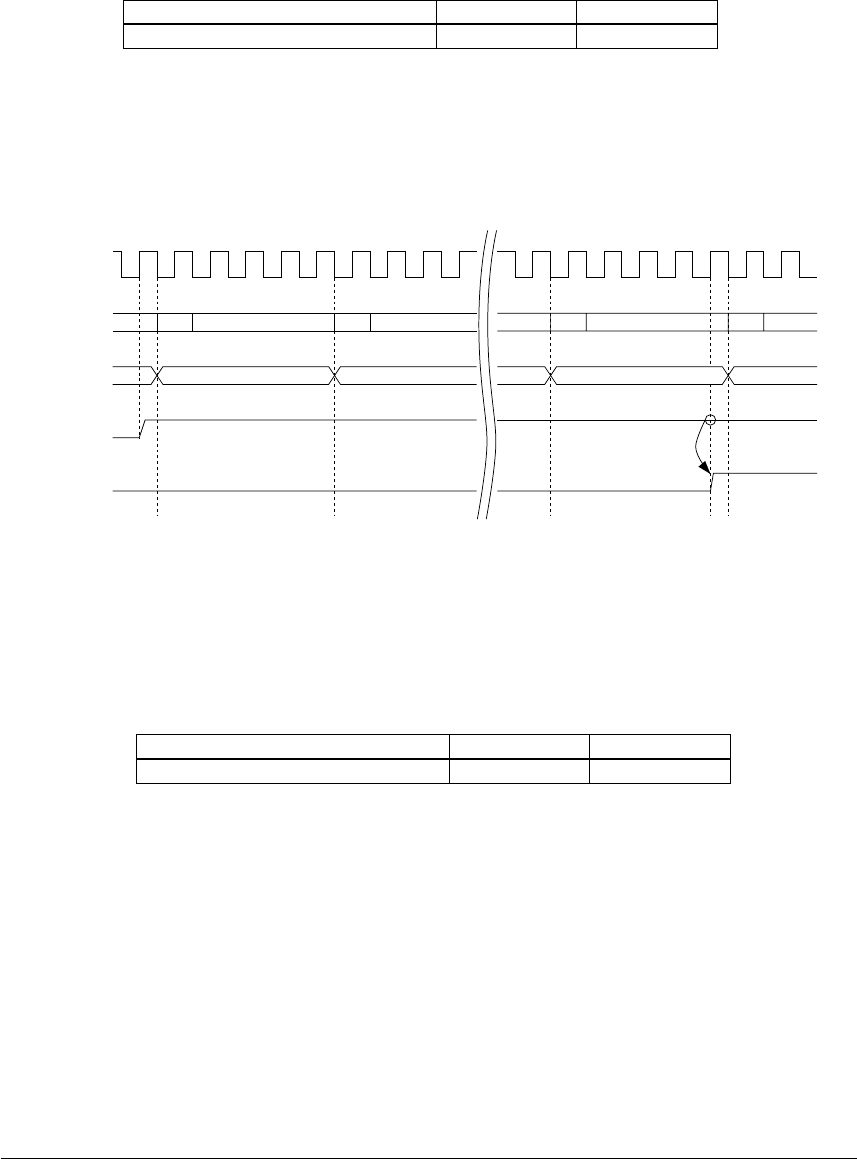

The operation during the instruction execution for writing "0" (i.e., to mask the interrupt factor) on the

interrupt mask register at EI is shown in Figure A2.2.2. At this point, the interrupt is masked 0.5 clock

before the start of the instruction execution through the 0.5 clock advance operation.

Moreover, during the instruction execution for writing "1" (i.e., to cancel the interrupt mask) on the mask

register at EI, it is the same as the ordinary interrupt timing as shown in Figure A2.2.2. In other words, if

the interrupt factor flag value is set to "1", the interrupt processing by hardware will start in the next

instruction execution cycle 0.5 clock before the completion of the instruction execution.

Fetch Execute Fetch Execute Fetch Execute Fetch

"0" is written to the interrupt mask register

Execute next instruction INT1(interrupt processing)

Clock

Status

Instruction

Corresponding

interrupt factor flag

Interrupt request

"1" is written to the interrupt mask register

Fig. A2.2.2 Writing on the interrupt mask register and interrupt request generation

<Reference 2> Reading the interrupt factor flag during EI

This section describes the operation for reading the interrupt factor flag during EI (enable interrupt flag) in

the regular 1-chip micro controller which uses S1C6200 Core CPU and in the regular 1-chip micro control-

ler which uses S1C6200A Core CPU. For information on accurate operation, see the respective hardware

manuals of the S1C62 Family.

Table A2.2.3 Reading the interrupt factor flag at EI

Reading the interrupt factor flag at EI

S1C6200

Not possible

S1C6200A

Possible

CPU Core

At EI, reading the interrupt factor flag is possible but caution must be observed in the following case: when

the value of the interrupt mask register corresponding to the interrupt factor flag which is to be read is set

to "1" (unmasked). In this case, interrupt request may be issued to the CPU due to the timing by which the

interrupt factor flag is set to "1", or the interrupt factor flag may be cleared by reading it and hence inter-

rupt request will not be issued.

Particularly when there are multiple interrupt factor flags in the same address, extra caution is required.