Application Note

(Includes Differences for 970FX to 970MP)

Preliminary IBM PowerPC

®

970MP RISC Microprocessor

AppNote_970FX-MP_Differences_Body.fm.1.0

November 15, 2006

5. Design Enhancements for PowerPC 970MP

Page 11 of 25

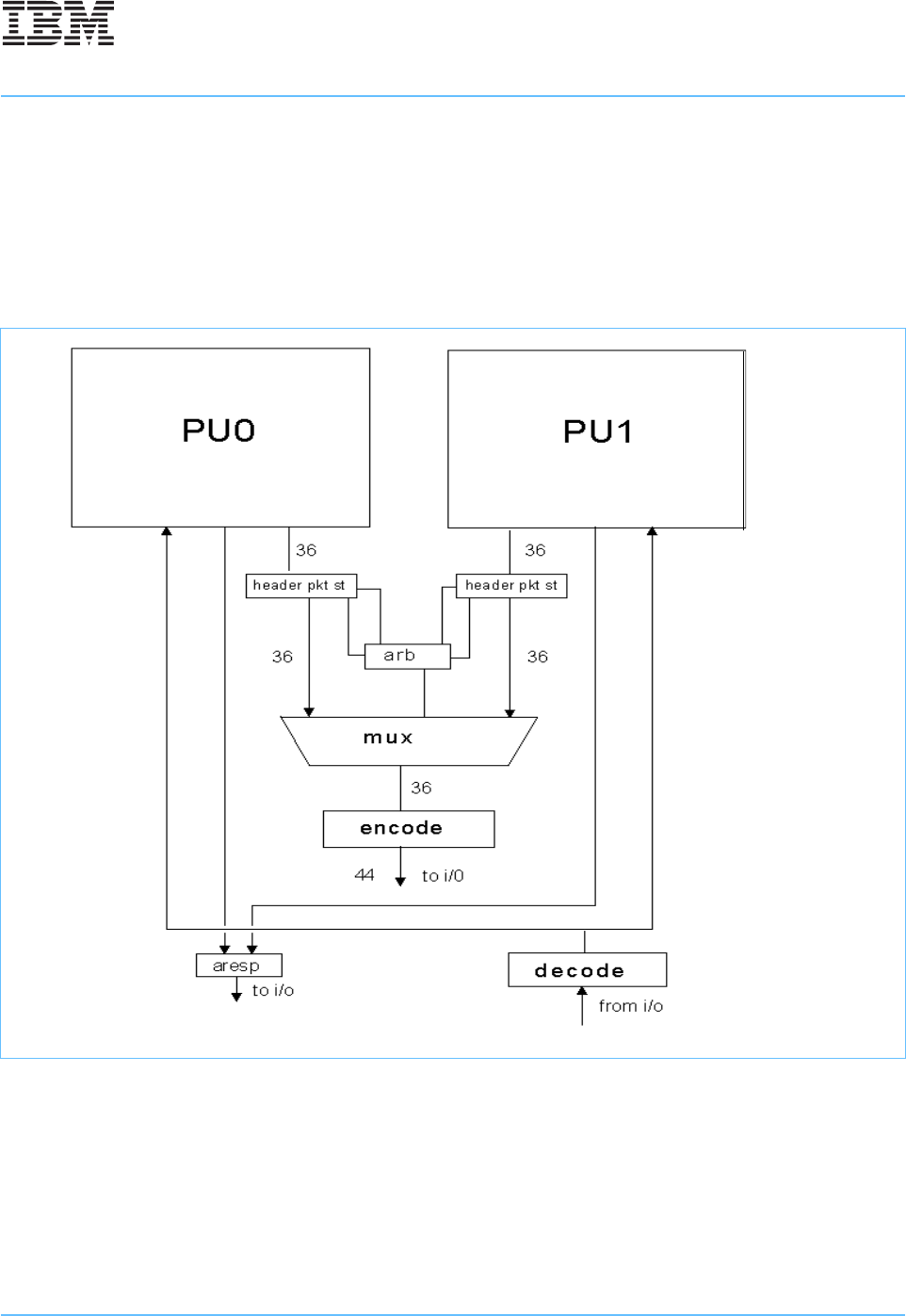

scheme, with provisions for adjusting priorities when one core receives repeated serial retries. Logic in the

BIU of each PU is modified to allow the arbiter to hold that PU from sending data to the PI bus when a trans-

action from the other processor is in progress. The PI bus configuration parameters apply to the single bus,

not to the individual processors, and so this arbiter enforces those parameters, such as the COMPACE

timing, for example. In order to minimize dead time on the bus, header packets for each processor are

queued at the arbiter. Finally, snoop responses from the two processors are combined on chip, and sent as a

single response over the PI bus to the bridge chip, as indicated in the lower left corner of Figure 5-1.

The additional logic at the PI/BIU interface requires a SNOOPLAT (and SNOOPACC) value that is larger than

for the 970FX, but still within the programmable range. The maximum STATLAT value on 970MP is increased

to 30, and it is expected that the bridge chip will need to similarly be designed for a higher maximum value

than was previously used. Refer to the IBM PowerPC 970MP Design Guidelines for more information.

Intercommunication between the processors on chip occurs in the same way as if they were on separate

chips, via the bridge chip. In particular, on-chip L2 to L2 intervention is not supported.

Figure 5-1. Dual Cores sharing processor interface