Application Note

(Includes Differences for 970FX to 970MP)

Preliminary IBM PowerPC

®

970MP RISC Microprocessor

AppNote_970FX-MP_Differences_Body.fm.1.0

November 15, 2006

5. Design Enhancements for PowerPC 970MP

Page 19 of 25

The transition from quarter to full frequency is handled in two stages. First, the processor is transitioned from

quarter frequency to half frequency using the quarter to half dither pattern. The processor is paused for 32

cycles at half frequency, and then transitioned to full frequency using the half to full dither pattern. A similar

procedure is used for the full to quarter frequency transition.

5.4.2 Programmable Delays for Power Saving Mode Transitions

The 970MP design introduces a programmable delay when transitioning between power saving modes, to

reduce di/dt in these cases. For example on interrupt, the processor transitions from Deep Nap, through Nap

and Doze, to Run. The latency is a combination of fixed (full frequency) and mesh clock cycles, plus a

programmable delay. The programmable delay, Dp, is controlled by a 6-bit mode ring value. Dp specifies the

number of full frequency cycles of delay from 0 to 63. This delay occurs 6 times during the Deep Nap to Run

transition.

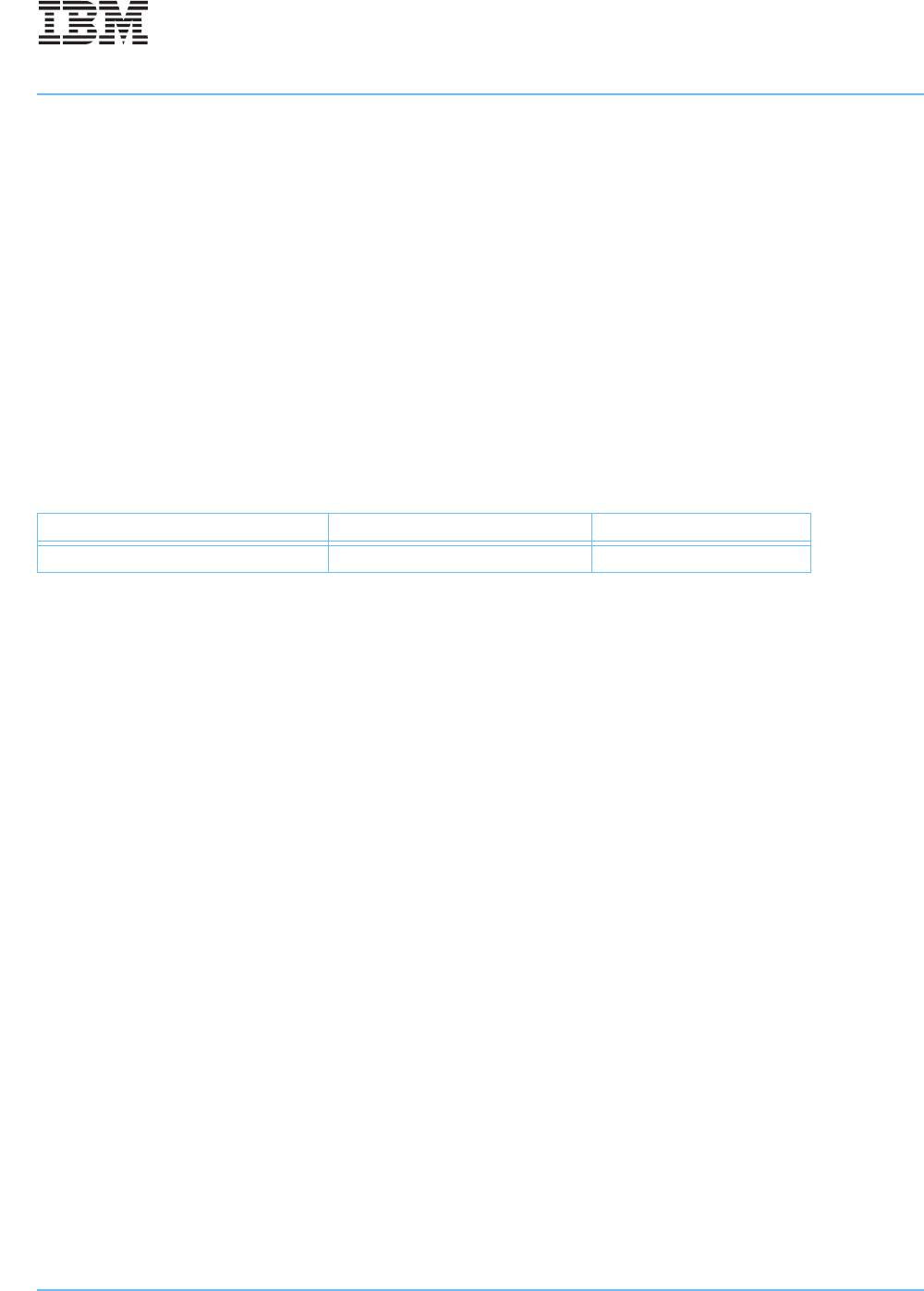

Table 5-3 lists the latency of Deep Nap to Run Transition for the PowerPC 970MP for full, half, and quarter

frequency scaling.

5.5 Additional Dynamic Power Management

To a limited extent the PowerPC 970 design implements dynamic power management (DPM) – the gating of

clocks to idle circuits while in an operational mode. For example, clocks in the pipelined vector processing

units (VPUs) are gated on a stage by stage basis, as instructions flow through the pipeline. The 970FX design

implements additional dynamic power management in the STS, IDU, and RAS units. The 970MP design

implements additional dynamic power management in the ISU, FXU, and FPU units.

Dynamic power management can be disabled as follows. For the VPU, IDU and STS, DPM is disabled by

negating HID0[DPM]. For the ISU, FXU, FPU and pervasive units, DPM is disabled by setting bit 0 in JTAG

register 0x00.0800 to a ‘1’.

5.6 More Precise Kelvin Circuitry

The 970MP implements circuitry that enables more precise Kelvin measurements. This increased precision

allows for better correlation between the Kelvin signals and the actual voltage applied to the transistors.

However, this improved precision in the Kelvin pins also increased their sensitivity. For DD1.0, DD1.01,

DD1.02, the maximum allowable current is 0.9mA. For DD1.1, the maximum allowable current is 2.7mA.

Exceeding these maximum currents may cause permanent damage to the microprocessor. Oscilloscope

probes should provide enough impedance to prevent excess current on these pins. Due to ESD concerns,

this change was reversed back to the 970FX implementation for DD1.03 and DD1.11+. For additional details,

refer to the IBM PowerPC 970MP RISC Microprocessor Datasheet.

Table 5-3. PowerPC 970MP Latency of Deep Nap to Run Transition (Full Frequency Cycles)

Full Half Quarter

123 + 6*Dp 228 + 6*Dp 438 + 6*Dp