Appendix A. Connector pin assignments 35

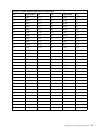

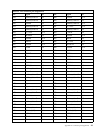

Table 20. System memory connector pin assignments

Pin x64 nonparity x72 ECC Pin x64 nonparity x72 ECC

1 VSS VSS 85 VSS VSS

2 DQ0 DQ0 86 DQ32 DQ32

3 DQ1 DQ1 87 DQ33 DQ33

4 DQ2 DQ2 88 DQ34 DQ34

5 DQ3 DQ3 89 DQ35 DQ35

6 VCC VCC 90 VCC VCC

7 DQ4 DQ4 91 DQ36 DQ36

8 DQ5 DQ5 92 DQ37 DQ37

9 DQ6 DQ6 93 DQ38 DQ38

10 DQ7 DQ7 94 DQ39 DQ39

11 DQ8 DQ8 95 DQ40 DQ40

12 VSS VSS 96 VSS VSS

13 DQ9 DQ 97 DQ41 DQ41

14 DQ10 DQ10 98 DQ42 DQ42

15 DQ11 DQ11 99 DQ43 DQ43

16 DQ12 DQ12 100 DQ44 DQ44

17 DQ13 DQ13 101 DQ45 DQ45

18 VCC VCC 102 VCC VCC

19 DQ14 DQ14 103 DQ46 DQ46

20 DQ15 DQ15 104 DQ47 DQ47

21 NC CB0 105 NC CB4

22 NC CB1 106 NC CB5

23 VSS VSS 107 VSS VSS

24 NC NC 108 NC NC

25 NC NC 109 NC NC

26 VCC VCC 110 VCC VCC

27 /WE /WE0 111 /CAS /CAS

28 DQMB0 DQMB0 112 DQMB4 DQMB4

29 DQMB1 DQMB1 113 DQMB5 DQMB5

30 /S0 /S0 114 NC /S1

31 DU NC 115 /RAS /RAS

32 VSS VSS 116 VSS VSS

33 A0 A0 117 A1 A1

34 A2 A2 118 A3 A3

35 A4 A4 119 A5 A5