Appendix A. Connector pin assignments 37

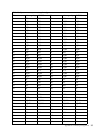

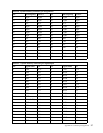

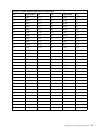

71 DQ26 DQ26 155 DQ58 DQ58

72 DQ27 DQ27 156 DQ59 DQ59

73 VCC VCC 157 VCC VCC

74 DQ28 DQ28 158 DQ60 DQ60

75 DQ29 DQ29 159 DQ61 DQ61

76 DQ30 DQ30 160 DQ62 DQ62

77 DQ31 DQ31 161 DQ63 DQ63

78 VSS VSS 162 VSS VSS

79 CK2 CK2 163 CK3 CK3

80 NC NC 164 NC NC

81 NC NC 165 SA0 SA0

82 SKA SDA 166 SA1 SA1

83 SCL SCL 167 SA2 SA2

84 VCC VCC 168 VCC VCC

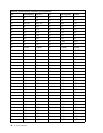

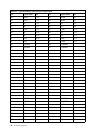

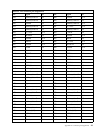

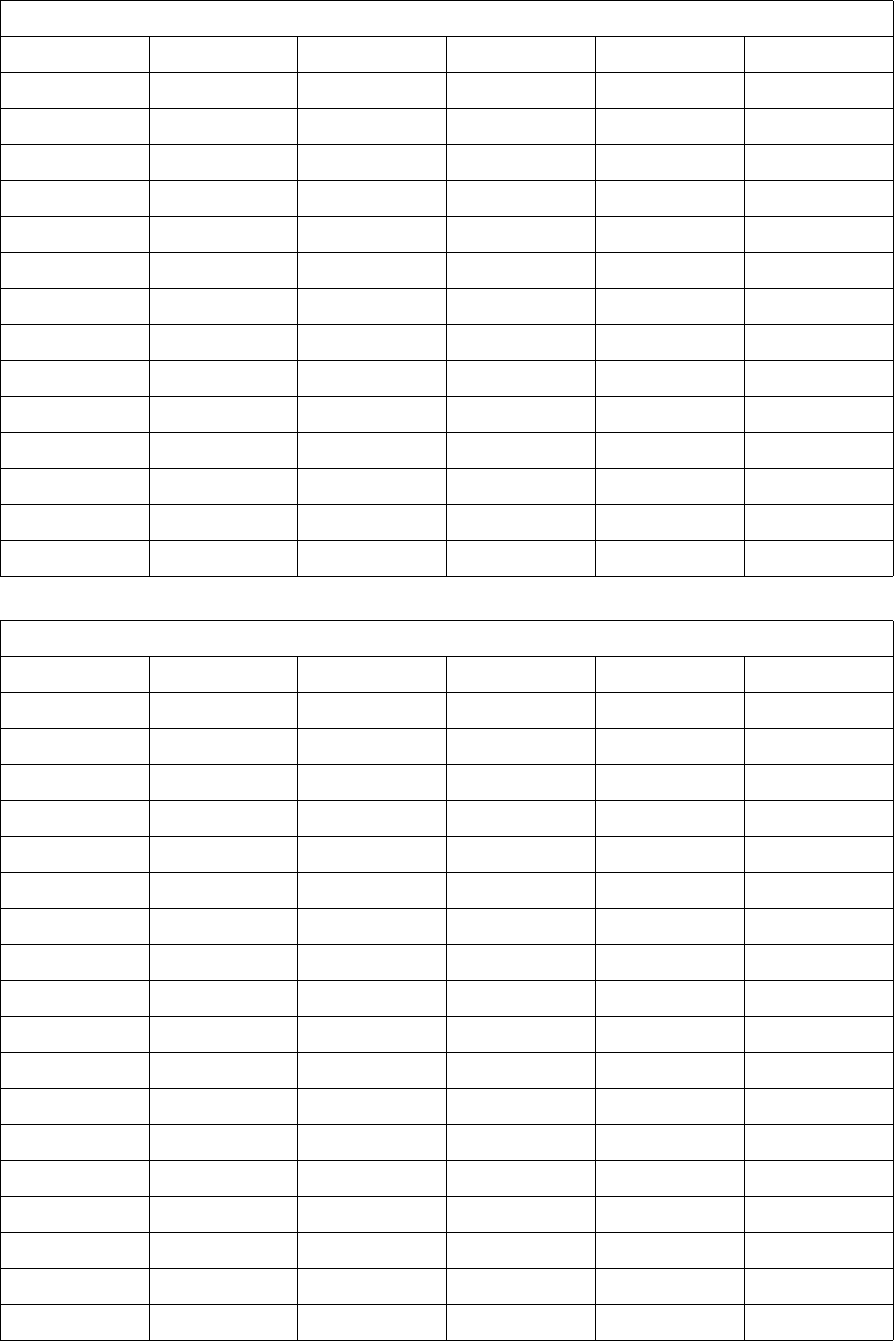

Table 21. System memory connector pin input/output

Pin Signal name I/O Pin Signal name I/O

1 GND N/A 85 GND N/A

2 MD0 I/O 86 MD32 I/O

3 MD1 I/O 87 MD33 I/O

4 MD2 I/O 88 MD34 I/O

5 MD3 I/O 89 MD35 I/O

6 VDD I/O 90 VDD N/A

7 MD4 I/O 91 MD36 N/A

8 MD5 I/O 92 MD37 I/O

9 MD6 I/O 93 MD38 I/O

10 MD7 I/O 94 MD39 I/O

11 MD8 (PAR0) I/O 95 MD40 I/O

12 GND N/A 96 GND N/A

13 MD9 I/O 97 MD41 I/O

14 MD10 I/O 98 MD42 I/O

15 MD11 I/O 99 MD43 I/O

16 MD12 I/O 100 MD44 I/O

17 MD13 I/O 101 MD45 I/O

18 VDD N/A 102 VDD N/A

Table 20. System memory connector pin assignments

Pin x64 nonparity x72 ECC Pin x64 nonparity x72 ECC