8086

Table 1 Pin Description

The following pin function descriptions are for 8086 systems in either minimum or maximum mode The ‘‘Local

Bus’’ in these descriptions is the direct multiplexed bus interface connection to the 8086 (without regard to

additional bus buffers)

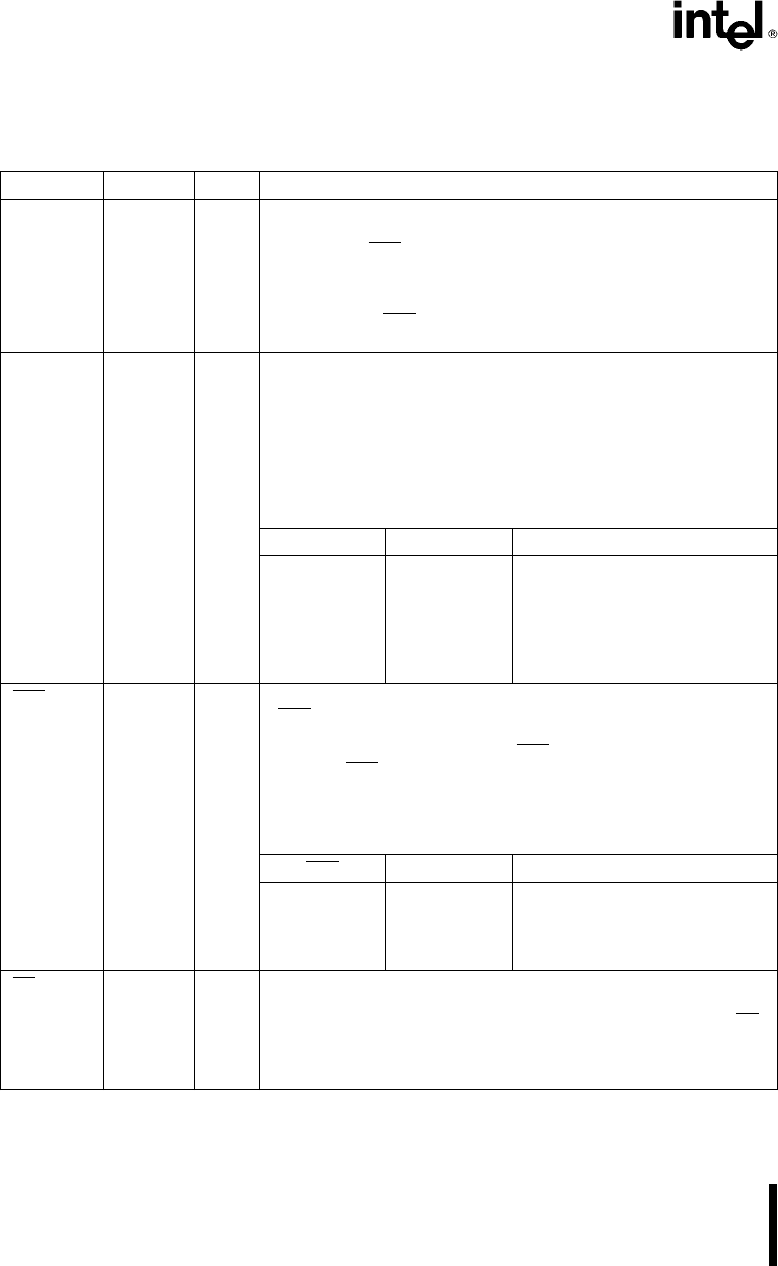

Symbol Pin No Type Name and Function

AD

15

–AD

0

2–1639 IO ADDRESS DATA BUS These lines constitute the time multiplexed

memoryIO address (T

1

) and data (T

2

T

3

T

W

T

4

) bus A

0

is

analogous to BHE

for the lower byte of the data bus pins D

7

–D

0

Itis

LOW during T

1

when a byte is to be transferred on the lower portion

of the bus in memory or IO operations Eight-bit oriented devices tied

to the lower half would normally use A

0

to condition chip select

functions (See BHE) These lines are active HIGH and float to 3-state

OFF during interrupt acknowledge and local bus ‘‘hold acknowledge’’

A

19

S

6

35–38 O ADDRESSSTATUS During T

1

these are the four most significant

address lines for memory operations During IO operations these

A

18

S

5

lines are LOW During memory and IO operations status information

A

17

S

4

is available on these lines during T

2

T

3

T

W

T

4

The status of the

A

16

S

3

interrupt enable FLAG bit (S

5

) is updated at the beginning of each

CLK cycle A

17

S

4

and A

16

S

3

are encoded as shown

This information indicates which relocation register is presently being

used for data accessing

These lines float to 3-state OFF during local bus ‘‘hold acknowledge’’

A

17

S

4

A

16

S

3

Characteristics

0 (LOW) 0 Alternate Data

0 1 Stack

1 (HIGH) 0 Code or None

1 1 Data

S

6

is 0

(LOW)

BHES

7

34 O BUS HIGH ENABLESTATUS During T

1

the bus high enable signal

(BHE

) should be used to enable data onto the most significant half of

the data bus pins D

15

–D

8

Eight-bit oriented devices tied to the upper

half of the bus would normally use BHE to condition chip select

functions BHE

is LOW during T

1

for read write and interrupt

acknowledge cycles when a byte is to be transferred on the high

portion of the bus The S

7

status information is available during T

2

T

3

and T

4

The signal is active LOW and floats to 3-state OFF in

‘‘hold’’ It is LOW during T

1

for the first interrupt acknowledge cycle

BHE A

0

Characteristics

0 0 Whole word

0 1 Upper byte fromto odd address

1 0 Lower byte fromto even address

1 1 None

RD 32 O READ Read strobe indicates that the processor is performing a

memory or IO read cycle depending on the state of the S

2

pin This

signal is used to read devices which reside on the 8086 local bus RD

is active LOW during T

2

T

3

and T

W

of any read cycle and is

guaranteed to remain HIGH in T

2

until the 8086 local bus has floated

This signal floats to 3-state OFF in ‘‘hold acknowledge’’

2