8086

FUNCTIONAL DESCRIPTION

General Operation

The internal functions of the 8086 processor are

partitioned logically into two processing units The

first is the Bus Interface Unit (BIU) and the second is

the Execution Unit (EU) as shown in the block dia-

gram of Figure 1

These units can interact directly but for the most

part perform as separate asynchronous operational

processors The bus interface unit provides the func-

tions related to instruction fetching and queuing op-

erand fetch and store and address relocation This

unit also provides the basic bus control The overlap

of instruction pre-fetching provided by this unit

serves to increase processor performance through

improved bus bandwidth utilization Up to 6 bytes of

the instruction stream can be queued while waiting

for decoding and execution

The instruction stream queuing mechanism allows

the BIU to keep the memory utilized very efficiently

Whenever there is space for at least 2 bytes in the

queue the BIU will attempt a word fetch memory

cycle This greatly reduces ‘‘dead time’’ on the

memory bus The queue acts as a First-In-First-Out

(FIFO) buffer from which the EU extracts instruction

bytes as required If the queue is empty (following a

branch instruction for example) the first byte into

the queue immediately becomes available to the EU

The execution unit receives pre-fetched instructions

from the BIU queue and provides un-relocated oper-

and addresses to the BIU Memory operands are

passed through the BIU for processing by the EU

which passes results to the BIU for storage See the

Instruction Set description for further register set

and architectural descriptions

MEMORY ORGANIZATION

The processor provides a 20-bit address to memory

which locates the byte being referenced The memo-

ry is organized as a linear array of up to 1 million

bytes addressed as 00000(H) to FFFFF(H) The

memory is logically divided into code data extra

data and stack segments of up to 64K bytes each

with each segment falling on 16-byte boundaries

(See Figure 3a)

All memory references are made relative to base ad-

dresses contained in high speed segment registers

The segment types were chosen based on the ad-

dressing needs of programs The segment register

to be selected is automatically chosen according to

the rules of the following table All information in one

segment type share the same logical attributes (eg

code or data) By structuring memory into relocat-

able areas of similar characteristics and by automati-

cally selecting segment registers programs are

shorter faster and more structured

Word (16-bit) operands can be located on even or

odd address boundaries and are thus not con-

strained to even boundaries as is the case in many

16-bit computers For address and data operands

the least significant byte of the word is stored in the

lower valued address location and the most signifi-

cant byte in the next higher address location The

BIU automatically performs the proper number of

memory accesses one if the word operand is on an

even byte boundary and two if it is on an odd byte

boundary Except for the performance penalty this

double access is transparent to the software This

performance penalty does not occur for instruction

fetches only word operands

Physically the memory is organized as a high bank

(D

15

–D

8

) and a low bank (D

7

–D

0

) of 512K 8-bit

bytes addressed in parallel by the processor’s ad-

dress lines A

19

–A

1

Byte data with even addresses

is transferred on the D

7

–D

0

bus lines while odd ad-

dressed byte data (A

0

HIGH) is transferred on the

D

15

–D

8

bus lines The processor provides two en-

able signals BHE

and A

0

to selectively allow read-

ing from or writing into either an odd byte location

even byte location or both The instruction stream is

fetched from memory as words and is addressed

internally by the processor to the byte level as nec-

essary

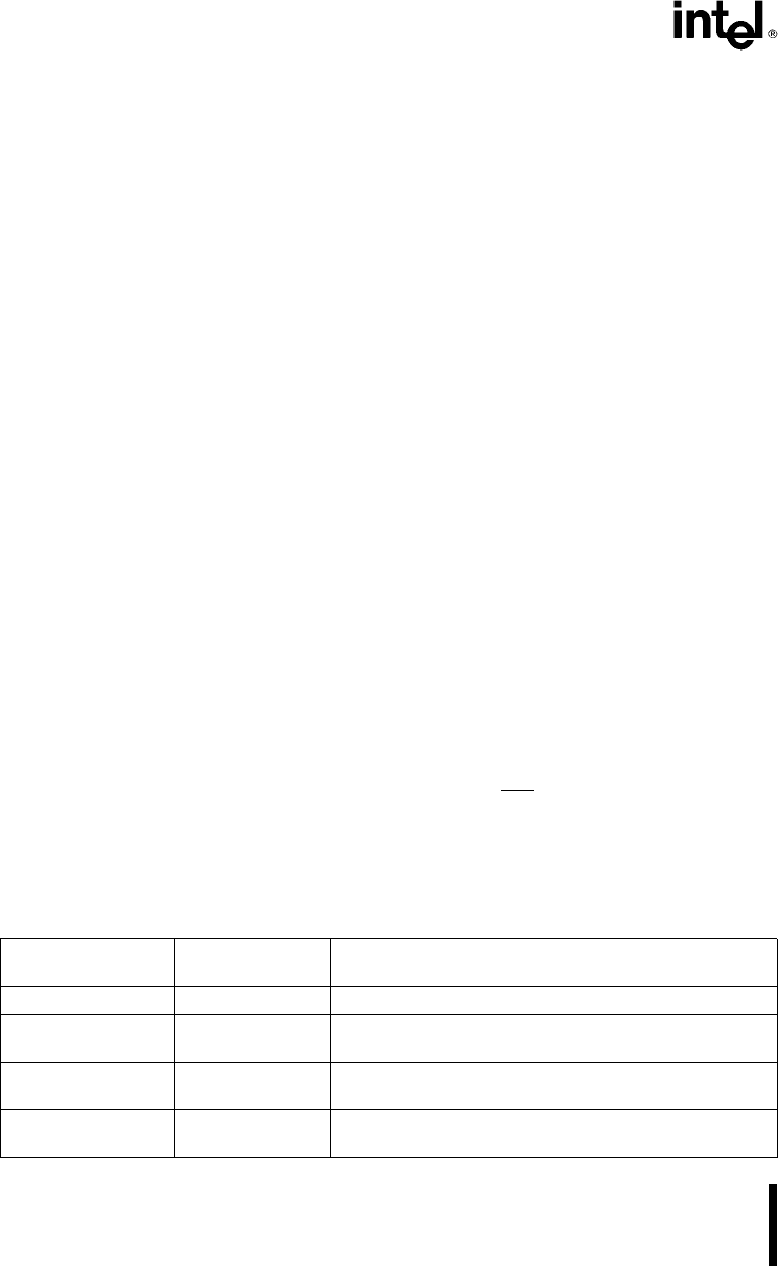

Memory Segment Register Segment

Reference Need Used Selection Rule

Instructions CODE(CS) Automatic with all instruction prefetch

Stack STACK (SS) All stack pushes and pops Memory references relative to BP

base register except data references

Local Data DATA(DS) Datareferences when relative to stack destination of string

operation or explicitly overridden

External (Global) Data EXTRA (ES) Destination of string operations explicitly selected using a

segment override

6