Software Developer’s Manual 105

EEPROM Interface

5.6.7 Initialization Control Word 1 (Word 0Ah)

The first word read by the Ethernet controller contains initialization values that:

• Sets defaults for some internal registers

• Enables/disables specific features

• Determines which PCI configuration space values are loaded from the EEPROM

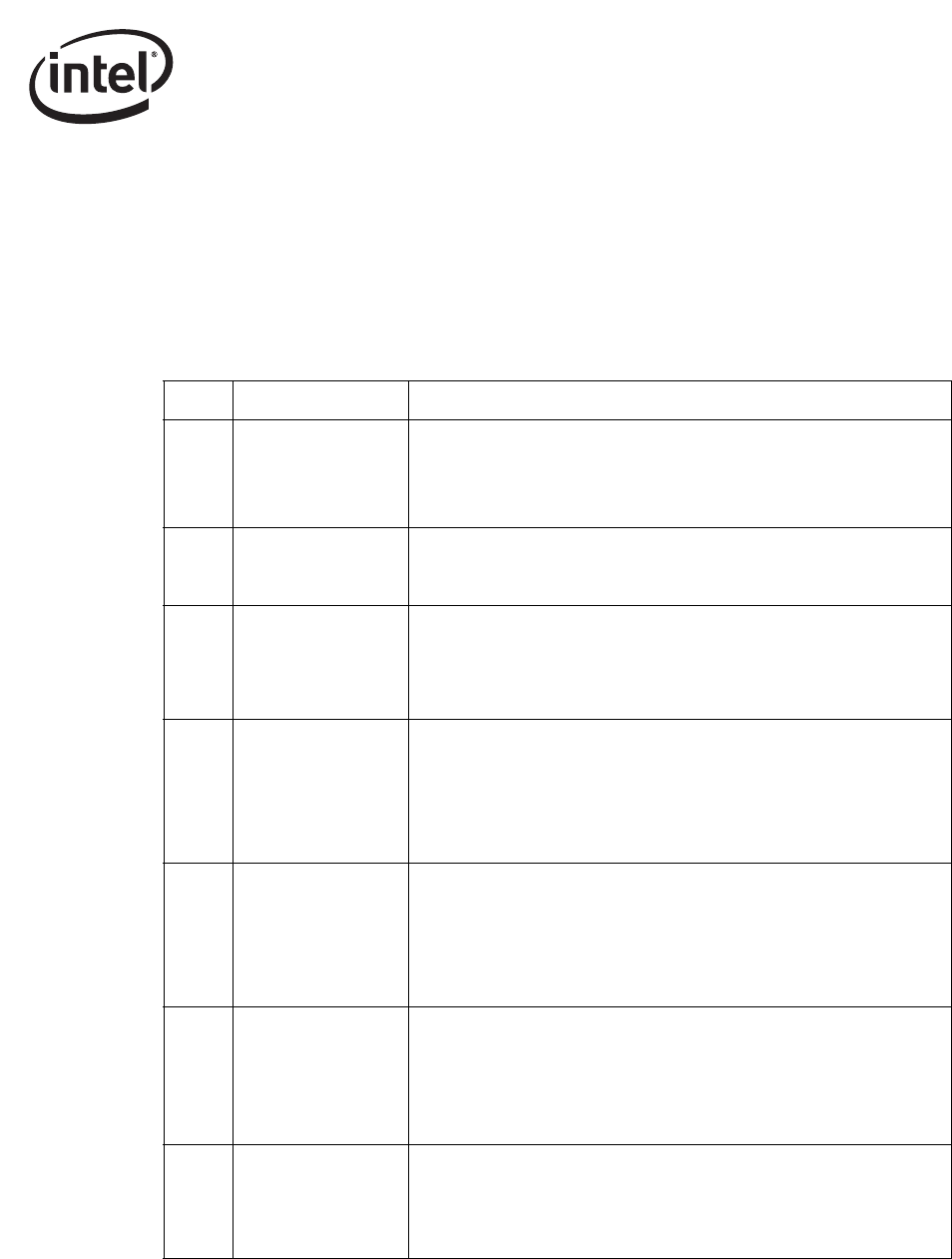

Table 5-5. Initialization Control Word 1 (Word 0Ah)

Bit Name Description

15:14 Signature

The Signature field represents a signature of 01b (default), indicating to the

Ethernet controller that there is a valid EEPROM present.

If the Signature field is not 01b, the other bits in this word are ignored, no

further EEPROM read is performed, and default values are used for the

configuration space IDs.

13 64/32 BAR

When set to 0b (default), enables 64-bit memory mapping.

When set to 1b, disables 64-bit memory mapping

Note: Set to 1b for the 82540EP/EM.

12 IPS0

When set to 0b (default), does not invert the Power State Output bit 0

(CTRL_EXT[14]).

When set to 1b, inverts the Power State Output invert bit 0

(CTRL_EXT[14]).

Note: Reserved bit for the 82541xx and 82547GI/EI (set to 0b).

11 FRCSPD

Force Speed bit in the Device Control register (CTRL[11]).

When set to 0b (default), does not force speed.

When set to 1b, forces speed (default for the 82540EP/EM).

For 10/100/1000 Mb/s systems using TBI mode (82544GC/EI)/internal

SerDes (82546GB/EB and 82545GM/EM)

a

, set this bit to 0b.

Note: Reserved bit for the 82541xx and 82547GI/EI (set to 0b).

10 FD

Full Duplex (mapped to CTRL[0] and TXCW[5]).

When set to 1b (default), enables full duplex (TBI mode/internal SerDes

only).

When set to 0b, disables full duplex (TBI mode only/internal SerDes).

Note: Reserved bit for the 82541PI/GI/EI and 82547GI/EI (set to 1b).

Note: Reserved bit for the 82541ER (set to 0b).

9LRST

Link Reset (mapped to CTRL[3]).

When set to 0b, enables Auto-Negotiation at power up or when asserting

RST# without driver intervention.

When set to 1b, disables Auto-Negotiation at power up or when asserting

RST# without driver intervention.

Note: Reserved bit for the 82541xx and 82547GI/EI (set to 0b).

8 IPS1

When set to 0b (default), does not invert the Power State Output bit 1

(CTRL_EXT[16]).

When set to 1b, inverts the Power State Output invert bit 1

(CTRL_EXT[16]).

Note: Reserved bit for the 82541xx and 82547GI/EI (set to 0b).