Software Developer’s Manual 275

Register Descriptions

13.4.7.1.17 Extended PHY Specific Control Register 1

1

EPSCON1 (20d; R/W)

1. Extended PHY Specific Control Register - EPSCON for the 82544GC/EI only.

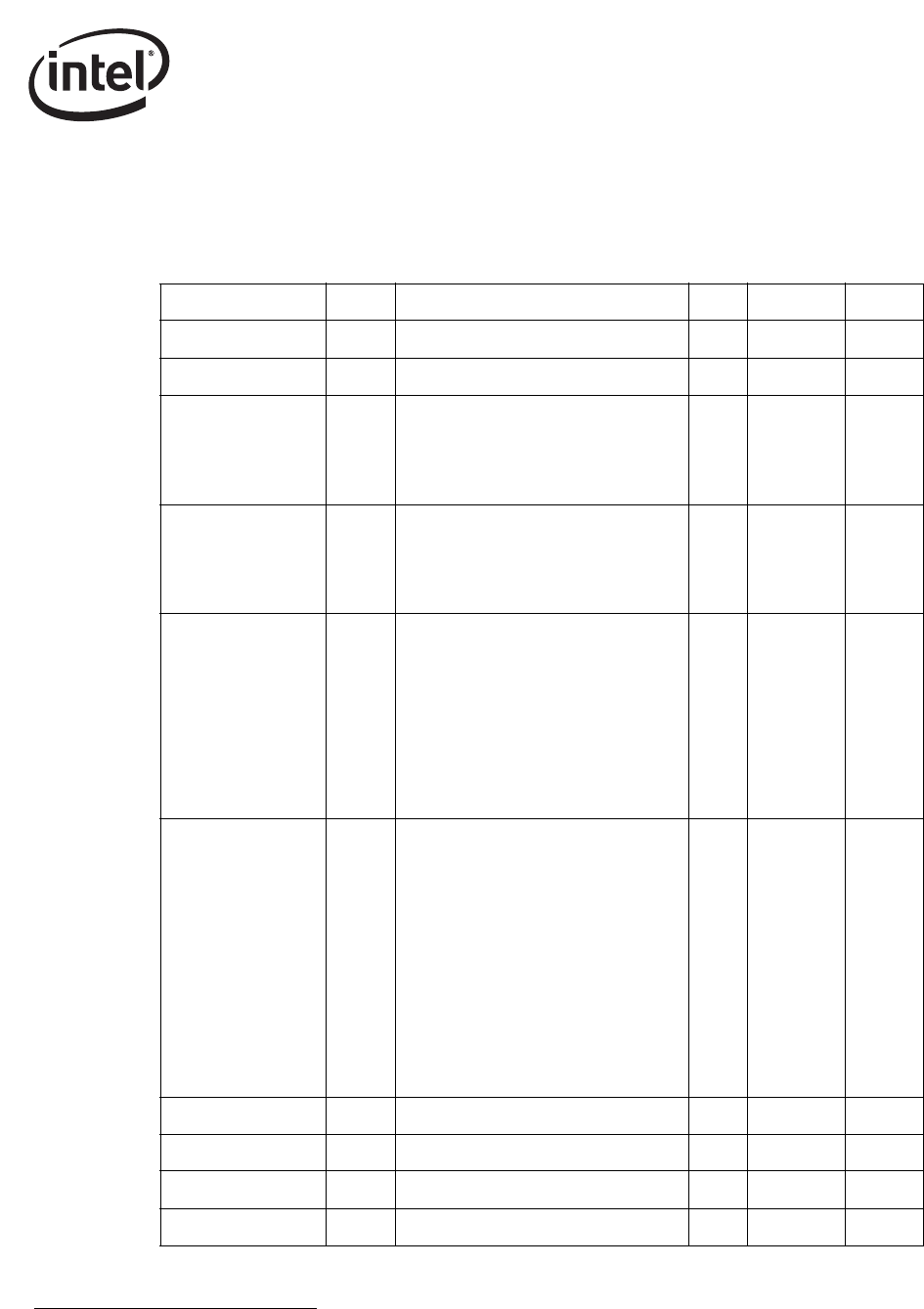

Table 13-39. Extended PHY Specific Control 1 Bit Description

1

Field Bit(s) Description Mode HW Rst SW Rst

Reserved 1:0 00b R/W 00b Retain

Reserved 3 0b R/W 0b 0

Reserved 6:4

Reserved. Should be set to 0b.

Changes to this bit are disruptive to the

normal operation; any change to this

register must be followed by software

reset to take effect.

R/W 110b Update

Reserved 7

Reserved. Should be set to 0b.

Changes to this bit are disruptive to the

normal operation; any change to this

register must be followed by software

reset to take effect.

R/W 0b Update

Slave downshift

counter

9:8

00b = disable. (10/100 downshift)

01b = 1x.

10b = 2x.

11b = 3x.

Changes to this bit are disruptive to the

normal operation; any change to this

register must be followed by software

reset to take effect.

Bits 11:10 have no effect unless bits 1:0

are set to their default values.

R/W 01b Update

Master downshift

counter

11:10

00b = 1x.

01b = 2x.

10b = 3x.

11b = 4x.

Number of times that the PHY attempts

to achieve gigabit link before

downshifting to the next speed in Master

Mode.

Changes to this bit are disruptive to the

normal operation; any change to this

register must be followed by software

reset to take effect.

Bits 11:10 have no effect unless bits 1:0

are set to their default values.

R/W 11b Update

Reserved 12 Reserved. Should be set to 0b. R/W 0b 0b

Reserved 13 Reserved. Should be set to 0b. R/W 0b 0b

Reserved 14 Reserved. Should be set to 0b. R/W 0b 0b

Reserved 15 Reserved. Should be set to 0b. R/W 0b 0b