Software Developer’s Manual 73

PCI Local Bus Interface

Cache Line Size

1

Used to store the cache line size. The value is in units of 4 bytes. A system with a

cache line size of 64 bytes sets the value of this register to 10h. The only sizes

that are supported are 16, 32, 64, and 128 bytes. All other sizes are treated as 0b.

See the information about exceptions in Section 4.4.

Unsupported values affect PCI cache line support. All writes default to using the

memory write (MW) command, and memory read command determination uses

a cache line size of 32 bytes.

Latency Timer The lower two bits are not implemented and return 0b. The upper six bits are

Read/Write.

Header Type This is for a normal single function Ethernet controller and reads 00h.

BIST Built in Self-test is not implemented as supportable from PCI configuration

space in this version of the Ethernet controller.

Base Address Registers

The Base Address Registers (or BARs) are used to map the Ethernet con-

troller’s register space and flash to system memory space. In PCI-X mode

or in PCI mode when the BAR32 bit of the EEPROM is 0b, two registers

are used for each of the register space and the flash memory in order to

map 64-bit addresses. In PCI mode, if the BAR32 bit in the EEPROM is

1b, one register is used for each to map 32-bit addresses.

64-bit BARs PCI-X mode with BAR32 bit in the EEPROM set to 0b.

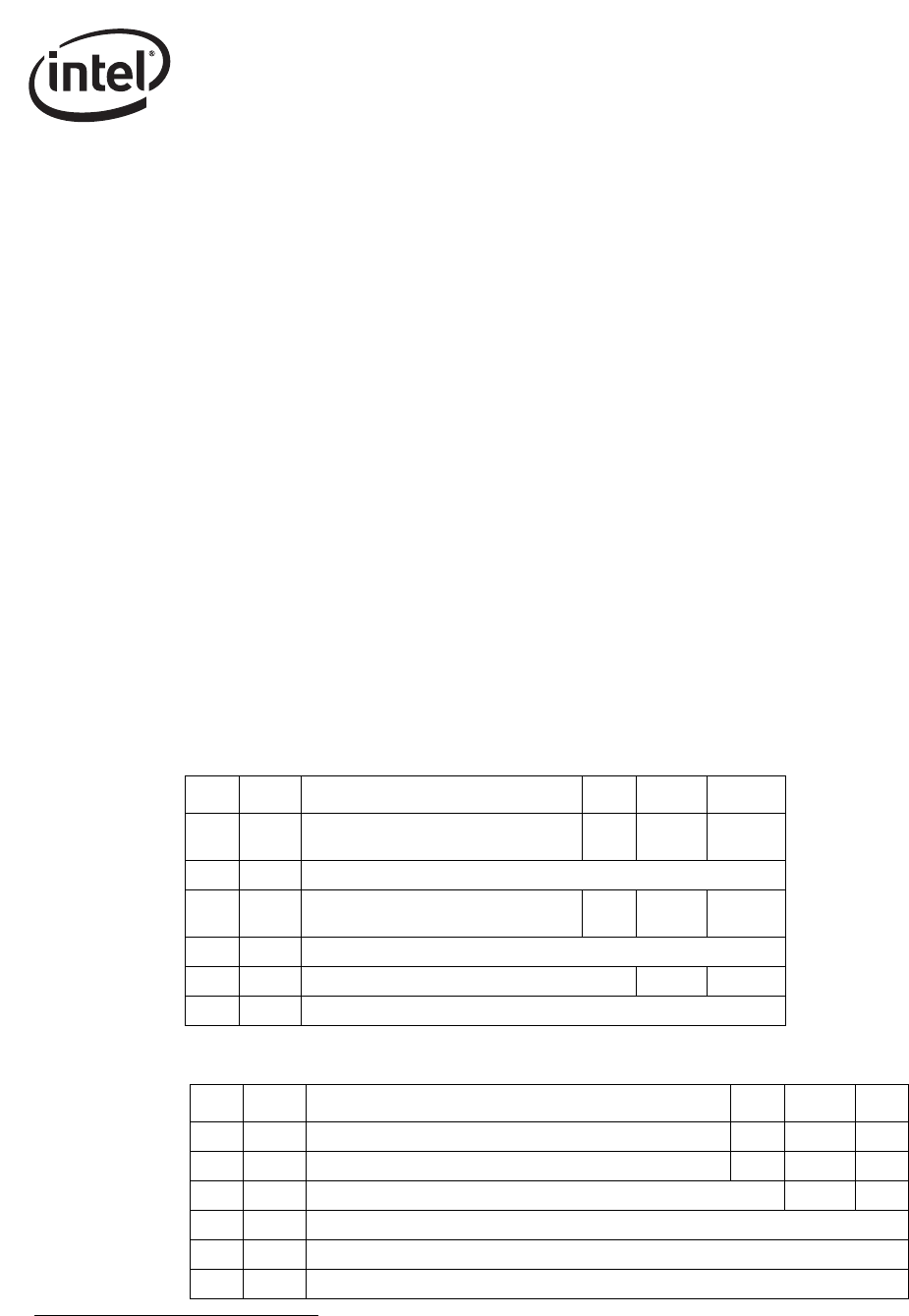

Table 4-2. Base Address Registers

32-bit BARs Conventional PCI mode with BAR32 bit in the EEPROM set to 1b

1. Not applicable to the 82547GI/EI.

BAR Addr. 31 4 3 2 1 0

0 10h

Memory Register Base Address (bits

31:4)

pref. type mem

1 14h Memory Register Base Address (bits 63:32)

2 18h

Memory Flash Base Address (bits

31:4)

pref. type mem

31ChMemory Flash Base Address (bits 63:32)

4 20h IO Register Base Address (bits 31:2) 0b mem

5 24h Reserved (read as all 0b’s)

BAR Addr. 31 4 3 2 1 0

0 10h Memory Register Base Address pref. type mem

1 14h Memory Flash Base Address pref. type mem

2 18h IO Register Base Address (bits 31:2) 0b mem

3 1Ch Reserved (read as all 0b’s)

4 20h Reserved (read as all 0b’s)

5 24h Reserved (read as all 0b’s)