Software Developer’s Manual 181

802.1q VLAN Support

In summary, the 4096 bit vector is composed of 128 32-bit registers. Matching to this bit vector

follows the same algorithm as indicated in Section 13.5.1 for Multicast Address filtering. The

VLAN Identifier (VID) field consists of 12 bits. The upper 7 bits of this field are decoded to

determine the 32-bit register in the VLAN Filter Table Array to address and the lower 5 bits

determine which of the 32 bits in the register to evaluate for matching.

Two other bits in the Receive Control register (see Section 13.4.22), CFIEN and CFI, are also used

in conjunction with 802.1q VLAN filtering operations. CFIEN enables the comparison of the value

of the CFI bit in the 802.1q packet to the Receive Control register CFI bit as an acceptance criteria

for the packet.

Note: The VFE bit does not affect whether the VLAN tag is stripped. It only affects whether the VLAN

packet passes the receive filter.

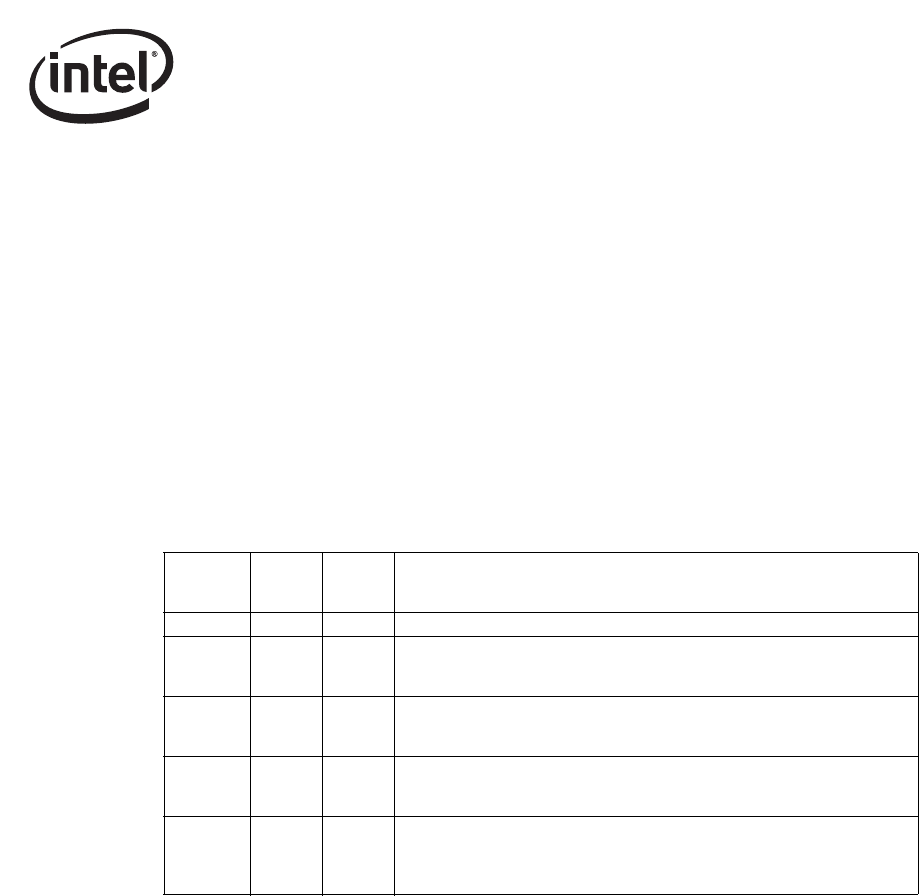

Table 9-3 lists reception actions according to control bit settings.

Table 9-3. Packet Reception Decision Table

Is

packet

802.1q?

CTRL.

VME

RCTL.

VFE

ACTION

No X X Normal packet reception.

Yes 0 0

Receive a VLAN packet if it passes the standard filters (only). Leave the

packet as received in the data buffer. Clear the VP bit in the receive

descriptor.

Yes 0 1

Receive a VLAN packet if it passes the standard filters and the VLAN

filter table. Leave the packet as received in the data buffer (the VLAN

tag is not stripped). Clear the VP bit in the receive descriptor.

Yes 1 0

Receive a VLAN packet if it passes the standard filters (only). Strip off

the VLAN information (four bytes) from the incoming packet and store in

the descriptor. Set the VP bit in the receive descriptor.

Yes 1 1

Receive a VLAN packet if it passes the standard filters and the VLAN

filter table. Strip off the VLAN information (four bytes) from the incoming

packet and store in the descriptor. Set the VP bit in the receive

descriptor.