Software Developer’s Manual 203

PHY Functionality and Features

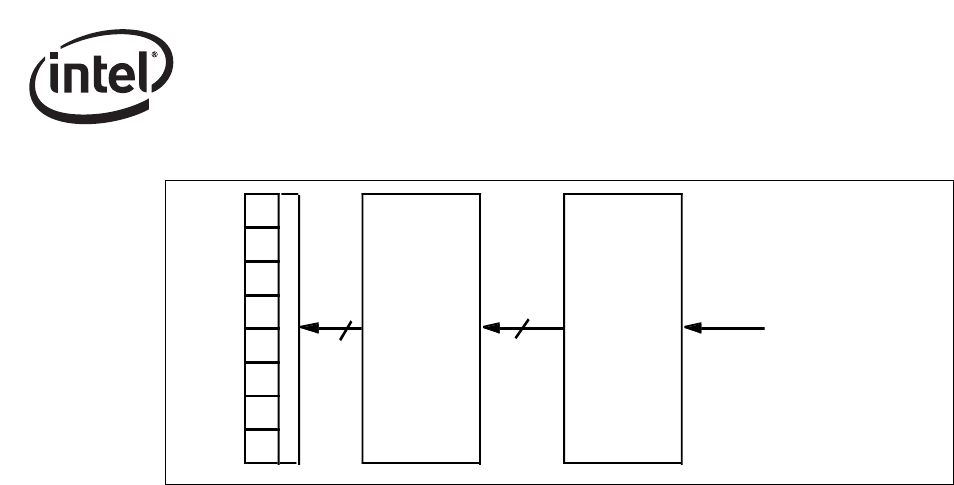

Figure 11-5. 1000BASE-T Receive Flow

11.11.4 Receive Functions

This section describes function blocks that are used when the PHY receives data from the twisted

pair interface and passes it back to the MAC.

11.11.4.1 Hybrid

The hybrid subtracts the transmitted signal from the input signal, allowing the use of simple

100BASE-TX compatible magnetics.

11.11.4.2 Automatic Gain Control

The Automatic Gain Control (AGC) normalizes the amplitude of the received signal, adjusting for

the attenuation produced by the cable.

11.11.4.3 Timing Recovery

This function re-generates a receive clock from the incoming data stream which is used to sample

the data. On the Slave side of the link, this clock is also used to drive the transmitter.

11.11.4.4 Analog-to-Digital Converter

The Analog-to-Digital (ADC) function converts the incoming data stream from an analog

waveform to digitized samples for processing by the DSP core.

11.11.4.5 Digital Signal Processor

The Digital Signal Processor (DSP) provides per-channel adaptive filtering, which eliminates

various signal impairments including:

• Inter-symbol interference (equalization).

• Echo caused by impedance mismatch of the cable.

• Near-end crosstalk (NEXT) between adjacent channels (A, B, C, D).

D0

D1

D2

D3

D4

D5

D6

D7

GMII

8 bits

Polynomial

Descrambler

8 bits

DSP

PAM-5

Encoded Input

from 4-Pair UTP Line

Receiver