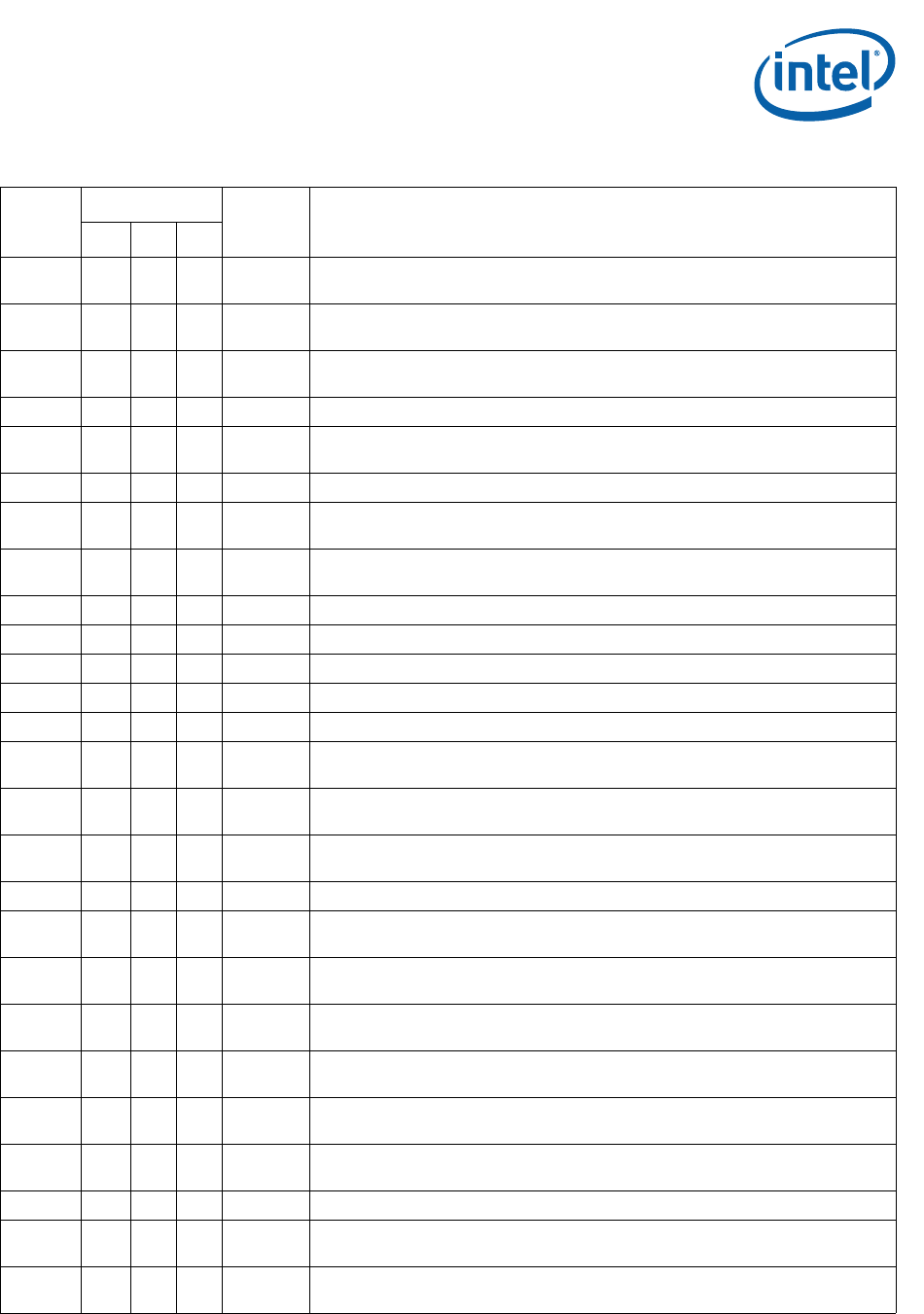

Specification Update 9

BV7

XXXNo Fix

General Protection Fault (#GP) for Instructions Greater than 15 Bytes May be

Preempted

BV8

XXXNo Fix

LBR, BTS, BTM May Report a Wrong Address when an Exception/Interrupt Occurs

in 64-bit Mode

BV9

XXXNo Fix

Incorrect Address Computed For Last Byte of FXSAVE/FXRSTOR or XSAVE/

XRSTOR Image Leads to Partial Memory Update

BV10

XXXNo FixValues for LBR/BTS/BTM Will be Incorrect after an Exit from SMM

BV11

XXXNo Fix

EFLAGS Discrepancy on Page Faults and on EPT-Induced VM Exits after a

Translation Change

BV12

XXXNo FixB0-B3 Bits in DR6 For Non-Enabled Breakpoints May be Incorrectly Set

BV13

XXXNo Fix

MCi_Status Overflow Bit May Be Incorrectly Set on a Single Instance of a DTLB

Error

BV14

XXXNo Fix

Debug Exception Flags DR6.B0-B3 Flags May be Incorrect for Disabled

Breakpoints

BV15

XXXNo FixLER MSRs May Be Unreliable

BV16

XXXNo FixStorage of PEBS Record Delayed Following Execution of MOV SS or STI

BV17

XXXNo FixPEBS Record not Updated when in Probe Mode

BV18

XXXNo FixMONITOR or CLFLUSH on the Local XAPIC's Address Space Results in Hang

BV19

XXXNo FixFaulting MMX Instruction May Incorrectly Update x87 FPU Tag Word

BV20

XXXNo Fix

An Uncorrectable Error Logged in IA32_CR_MC2_STATUS May also Result in a

System Hang

BV21

XXXNo Fix

#GP on Segment Selector Descriptor that Straddles Canonical Boundary May Not

Provide Correct Exception Error Code

BV22

XXXNo Fix

DR6.B0-B3 May Not Report All Breakpoints Matched When a MOV/POP SS is

Followed by a Store or an MMX Instruction

BV23

XXXNo FixAPIC Error “Received Illegal Vector” May be Lost

BV24

XXXNo Fix

Changing the Memory Type for an In-Use Page Translation May Lead to Memory-

Ordering Violations

BV25

XXXNo Fix

Reported Memory Type May Not Be Used to Access the VMCS and Referenced

Data Structures

BV26

XXXNo Fix

LBR, BTM or BTS Records May have Incorrect Branch From Information After an

EIST/T-state/S-state/C1E Transition or Adaptive Thermal Throttling

BV27

XXXNo Fix

Fault Not Reported When Setting Reserved Bits of Intel® VT-d Queued Invalidation

Descriptors

BV28

XXXNo Fix

FP Data Operand Pointer May Be Incorrectly Calculated After an FP Access Which

Wraps a 4-Gbyte Boundary in Code That Uses 32-Bit Address Size in 64-bit Mode

BV29

XXXNo Fix

VMREAD/VMWRITE Instruction May Not Fail When Accessing an Unsupported

Field in VMCS

BV30

XXXNo FixSpurious Interrupts May be Generated From the Intel® VT-d Remap Engine

BV31

XXXNo Fix

Malformed PCIe Transactions May be Treated as Unsupported Requests Instead of

as Critical Errors

BV32

XXXNo Fix

Reception of Certain Malformed Transactions May Cause PCIe Port to Hang

Rather Than Reporting an Error

Errata (Sheet 2 of 5)

Number

Steppings

Status ERRATA

E-1 L-1 N-0