82543GC Gigabit Ethernet Controller Specification Update

21

SPECIFICATION CLARIFICATIONS

1. 0-70C Ambient Temperature Range

Problem: The data sheet contains conflicting information on the controller’s rated temperature range. The recommended

temperature range is given as 0-55C both in a specification table and Section 5.3, Thermal Specifications.

Elsewhere, the data sheet indicates a recommended maximum junction temperature of 100C and mentions 0-

70C as a test footnote.

Intel validated the 82543GC Gigabit Ethernet Controller for the full commercial ambient temperature range of 0-

70C. The overriding specification is the 100C maximum junction temperature. Multiplying the typical 1.5W

power by the 17C/W thermal coefficient, then adding the product to 70, yields approximately 96C, which falls

under the 100C limit.

Affected Specs: Recommended Operating Conditions and the Thermal Specifications section of OR-2711 82543GC Gigabit

Ethernet Controller Advance Information Datasheet Rev. 2.01. Documentation will change to uniformly indicate

0-70C.

2. Receiver Enabling and Disabling

Problem: The 82543GC controller does not support “throttled” reception by repeatedly disabling/enabling the receiver by

programming the Enable (EN) Bit in the Receive Control Register (RCTL). The reason is that the

disabling/enabling operation does not re-initialize packet filter logic that demarcates packet start and end

locations in the FIFO.

A note will be added to the RCTL register description reminding users to reset at least the receiver before re-

enabling it.

Affected Specs: RCTL register description in OR-2710 82543GC Gigabit Ethernet Controller Developer’s Manual Rev. 2.01.

DOCUMENTATION CHANGES

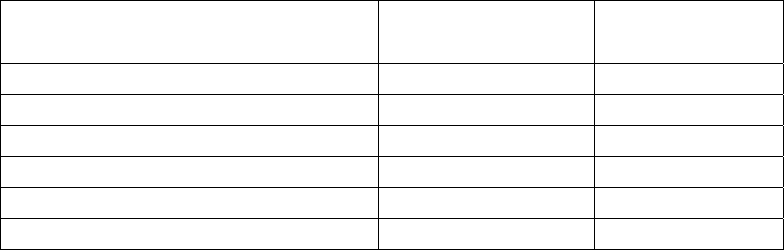

1. TX/RX Descriptor Register Addresses

Problem: The 82543GC Gigabit Ethernet Controller cannot use address offsets assigned for the previous generation

82542 Gigabit Ethernet Controller. Affected registers include the transmit descriptor registers (incorrect offset

range 0x420 – 0x440), receive descriptor registers, diagnostic packet buffer head/tail registers (incorrect offset

range 0x8000 – 0x8018) and the flow control threshold registers (incorrect offset range 0x160 – 0x168).

Offsets for these registers will change in documentation to reflect the correct 82543GC device values. Refer to

the following table for specific changes.

Register Name Incorrect Offsets

(Based on 82542

Controller)

Corrected Offsets

(Based on 82543GC

Controller)

RX_DELAY_TIMER 00108 02820

RX_DESC_BASE_ADDR 00110 02800

RX_RING_LENGTH 00118 02808

RX_DESC_HEAD 00120 02810

RX_DESC_TAIL 00128 02818

TX_DESC_BASE_ADDR 00420 03800