82543GC Gigabit Ethernet Controller Specification Update

9

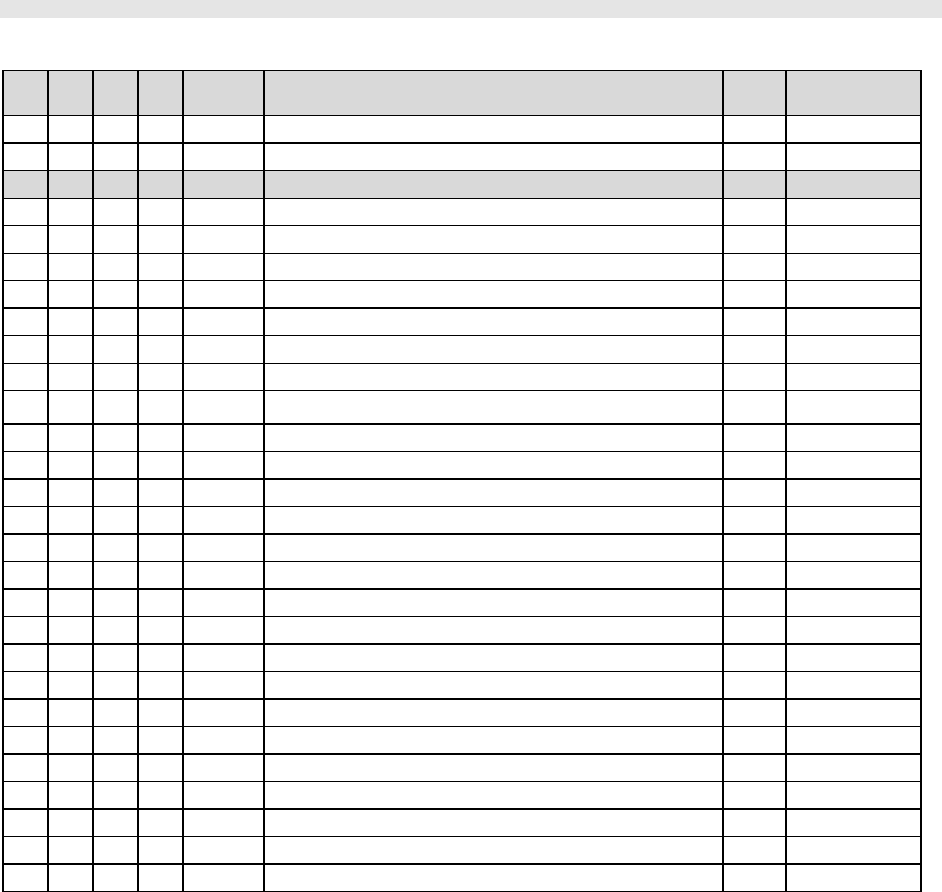

Summary Table of Changes

The following table indicates the Specification Changes, Errata, Specification Clarifications or Documentation Changes, which apply

to the listed 82543GC steppings. Intel intends to fix some of the errata in a future stepping of the component, and to account for the

other outstanding issues through documentation or Specification Changes as noted. This table uses the following notations:

CODES USED IN SUMMARY TABLES

X: Erratum, Specification Change or Clarification that applies to this stepping.

Doc: Document change or update that will be implemented.

Fix: This erratum is intended to be fixed in a future stepping of the component.

Fixed: This erratum has been previously fixed.

NoFix: There are no plans to fix this erratum.

(No mark) or (Blank Box): This erratum is fixed in listed stepping or specification change does not apply to listed stepping.

Shaded: This item is either new or modified from the previous version of the document.

No. A0 A1 A2 Plans SPECIFICATION CHANGES Page Affected

Document

1 X X X NoFix GMII Setup and Hold Times 9 Datasheet

No. A0 A1 A2 Plans ERRATA Page Notes

1 X X X NoFix MDI Control Register Returns Incorrect Values 9

2 X X X NoFix Descriptor Queue Maximum Size Limitation 9

3 X Fixed Late Collision Statistics May Be Incorrect 9

4 X Fixed Some Registers Cannot be Accessed During Reset 10

5 X X X NoFix DAC Accesses May Not Be Interpreted Correctly 10

6 X X X NoFix Flash Memory Functions Incorrectly in 64-Bit Address Space 10

7 X Fixed Excessive Errors in 100Mb Half-Duplex Mode 10

8 X Fixed 48 Bit Preambles Sent in 10Mb and 100Mb Operation 11

9 X Fixed CRS Detection Takes Too Long in MII Half-Duplex Mode 11

10 X X X NoFix DMA Early Receive Function Does Not Work 11

11 X Fixed ILOS Bit Copied Incorrectly from EEPROM to Speed Bits 11

12 X X X NoFix Gigabit Half-Duplex Mode Operates Incorrectly 11

13 X X X NoFix Zero-Byte PCI Bus Writes 12

14 X X X NoFix TCP Segmentation Feature Operates Incorrectly 12

15 X X Fixed Incorrect Checksum Calculation and Indication 12

16 X Fixed Transmitter Affected by Discarding Packets 12

17 X Fixed Flash Memory Address Conflicts 13

18 X X X NoFix Packet Buffer Memory Address Conflicts 13

19 X Fixed Transmit Packet Corruption of Small Packets 13

20 X Fixed Receive Packet Buffer Corruption When Nearly Full 13

21 X X Fixed Receive Packet Loss in 100Mb Half-Duplex Operation 14

22 X X X NoFix TNCRS Statistic Register Has Live Count in Full-Duplex Mode 14

23 X NoFix Receive IP Checksum Offload Disabled 14

24 X X X NoFix EEPROM Initializes Software Defined Pins Incorrectly 14

25 X X X NoFix Continuous XOFFs Transmitted When Receive Buffer Is Full 15