82543GC Gigabit Ethernet Controller Specification Update

22

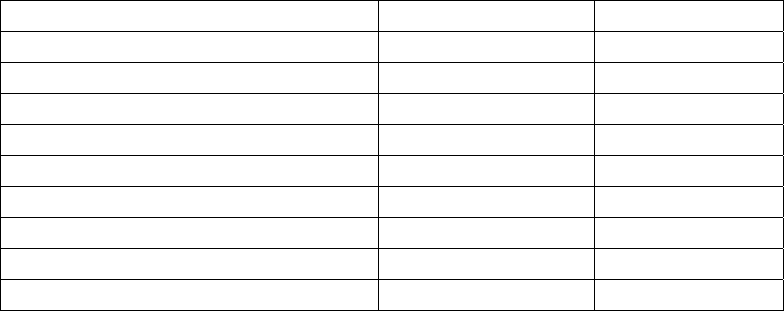

TX_RING_LENGTH 00428 03808

TX_DESC_HEAD 00430 03810

TX_DESC_TAIL 00438 03818

TX_INTERRUPT_DELAY 00440 03820

RX_PB_HEAD 08000 02410

RX_PB_TAIL 08008 02418

TX_PB_HEAD 08010 03410

TX_PB_TAIL 08018 03418

FLOW_CONTROL RX THRESH HI 00160 02168

FLOW_CONTROL RX THRESH LO 00168 02160

Affected Docs: 82543GC Gigabit Ethernet Controller Developer’s Manual, Order #751596-001. Note: this is an obsolete

document. It has been replaced by the combined data sheet/developer’s manual documents indicated in the

preface of this spec update.

2. Auto Speed Detect Function Requires CTRL.SLU Bit to Be Set

Problem: Setting the Set Link Up (SLU) bit is a prerequisite for the Auto Speed Detect Enable (ASDE) bit in the Device

Control Register to operate correctly. Asserting CTRL.SLU does not actually force link-up unless the link

indication input indicates that the 82543GC device is connected to a PHY device with valid link.

Documentation will change to explain the complete behavior.

Affected Docs: 82543GC Gigabit Ethernet Controller Developer’s Manual, Order #751596-001. Note: this is an obsolete

document. It has been replaced by the combined data sheet/developer’s manual documents indicated in the

preface of this spec update.

3. Values Programmed to Some Registers While in Reset Do Not Persist

Problem: This behavior is related to erratum #4, Some Registers Cannot Be Accessed During Reset. The erratum was

corrected, preventing infinite PCI retries, but values in certain registers will not be retained after the reset state

ends. Documentation will change to explain which registers are affected.

Affected Docs: 82543GC Gigabit Ethernet Controller Developer’s Manual, Order #751596-001. Note: this is an obsolete

document. It has been replaced by the combined data sheet/developer’s manual documents indicated in the

preface of this spec update.

4. JTAG Port Operation

Problem: The JTAG interface as described in the Developer’s Manual is not compliant to the IEEE 1149.1 specification

and only supports the IDCODE instruction. However, the pin description tables in the datasheet (also the text in

the Developer’s Manual) does not describe the capabilities of this interface and some readers may think that full

boundary scan is supported.

The pin description tables and text will change so the function is described as the “Test Access Port (IDCODE

function)” instead of “JTAG”.

Affected Docs: OR-2711 82543GC Gigabit Ethernet Controller Advance Information Datasheet Rev. 2.01 and OR-2710

82543GC Gigabit Ethernet Controller Developer’s Manual Rev. 2.01.