Intel

®

IQ31244 Customer Reference Board

User’s Manual 15

2.1 PAL Arbitration Circuit

The IQ31244 provides a Programmable Analog Logic (PAL) arbitration circuit on the primary

PCI-X bus. A rotating priority arbitration scheme with a host and three agents is used. The priority

rotates as shown in Table 7. The arbiter evaluates all requests and grants the bus to the highest-

priority requesting device. On reset, the host is granted the bus, and agent 0 (PCI-X bridge) has the

next-highest priority.

When an agent is “skipped”, priority is not returned to that agent until the next passing cycle. This

means that the agent is dropped from the highest priority to the lowest priority.

The arbiter has a time-out feature that functions as follows. Any PCI master which has requested

the bus, but has not started an access within 16 clocks of receiving a grant, is assumed to be broken

and the grant is rescinded.

When the PCI bus arbiter receives a request for the bus and there are currently no active

transactions on the bus, the arbiter immediately grants ownership to the requester.

When two or more requests are active, the bus is granted to the requester with the higher priority.

This approach ensures that all requesters are able to gain access to the bus in a reasonable time and

that a high-bandwidth PCI adapter cannot starve all other requesters off the bus. This arbitration

scheme conforms to the fairness doctrine described in the PCI Bus Specification, Revision 2.2.

The arbiter also implements bus parking. After a transaction is complete, if there are no requests

for the bus, the arbiter parks the bus at the last owner. When that device wishes to begin another

PCI transaction, it may do so without first requesting the bus. When another device requests the

bus, the arbiter can immediately remove bus ownership from the idle device where it is parked.

After reset or power-up the PCI bus is parked at the host.

Highest arbitration priority is given to the host immediately succeeding the bus owner, active or

parked. Bus ownership is passed to the host with the next-highest priority and with an active bus

request.

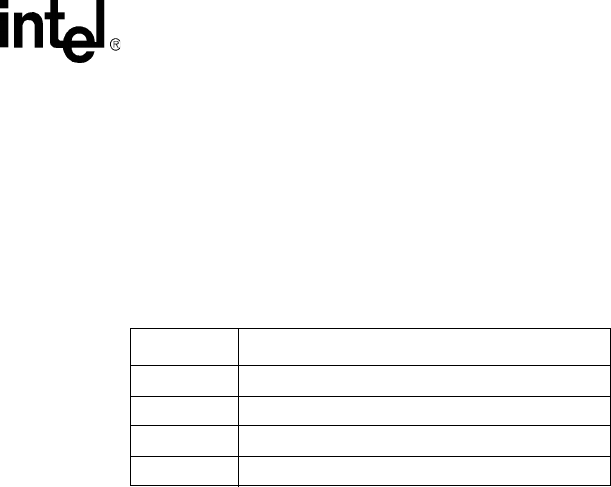

Table 7. Rotation Scheme of the PAL Arbitration Circuit

Priority Description

Host Intel

®

80321 I/O Processor

0 Intel

®

31154 133 MHz PCI Bridge

1 Expansion slot

2 Intel

®

82546 Dual-Port Gigabit Ethernet Controller