Board Manual 55

Intel® IQ80219 General Purpose PCI Processor Evaluation Platform

Hardware Reference Section

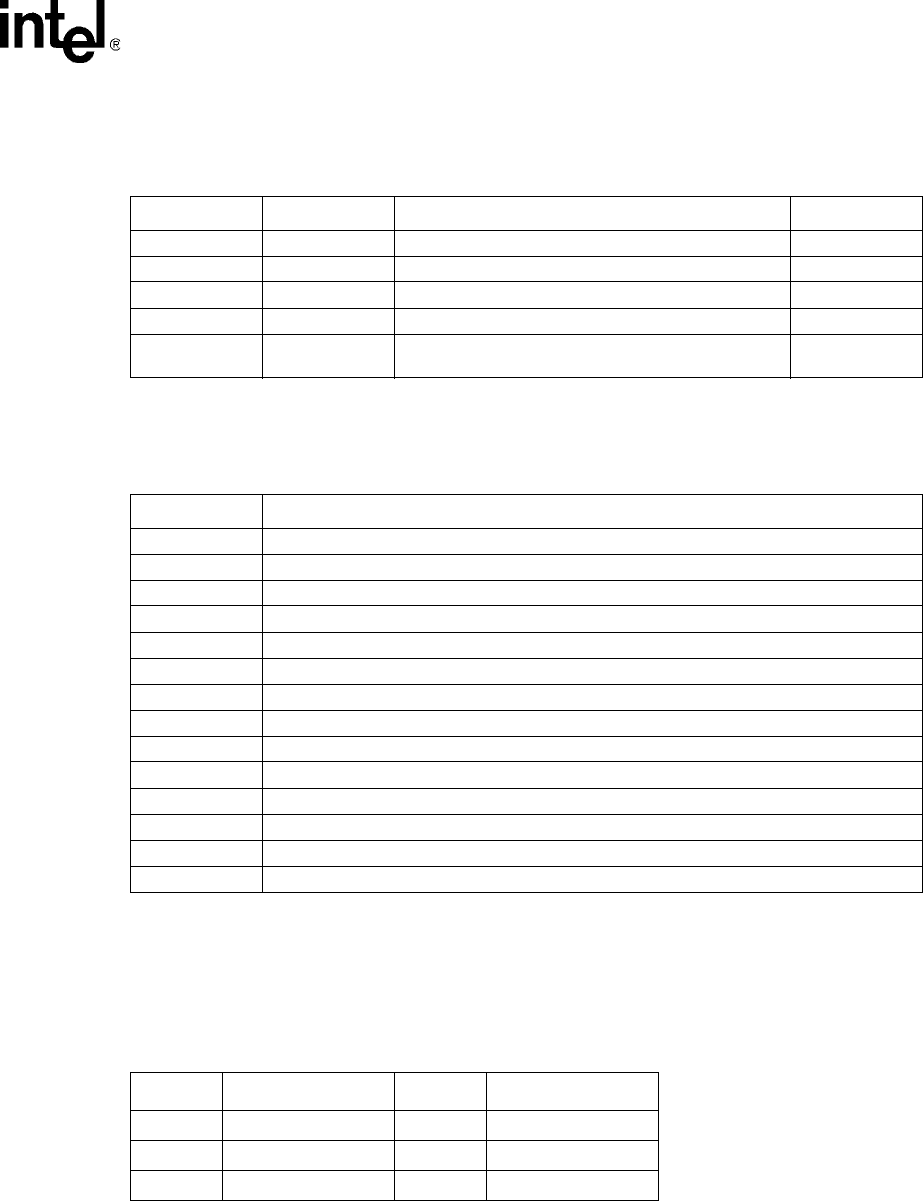

3.10.4 Jumper Summary

3.10.5 Connector Summary

3.10.6 General Purpose Input/Output Header

The board has three programmable general-purpose I/O pins (GPIO 0-3 on the 80321). These pins are

connected to a 6-pin, 2.54 mm (0.100") header (connector J3F1).

Table 31. Jumper Summary

Jumper Association Description Factory Default

J1G2 PPCI-X Reset Can isolated the PCI-X reset from getting to the board. 2-3

J3E1 SPCI-X Clock Enables spread-spectrum on the SPCI-X clock. 2-3

J3G1 PCI-X Bridge Enables Bridge access from the SPCI-X side. 2-3

J9E1 PCI-X Bridge Enables Base Address Register (BAR). 2-3

J9F1 PCI-X Bridge

Allows user to control initialization sequence on the

bridge.

2-3

Table 32. Connector Summary

Connector Description

J1F1 RJ45 Network Connector for GbE NIC

J1G1 RJ11 Serial Port Connector for UART

J7A1 20-Pin JTAG Debug Connector

J1C1 Logic analyzer Mictor Connector for SPCI-X Bus

J2C1 Logic analyzer Mictor Connector for SPCI-X Bus

J3C1 Logic analyzer Mictor Connector for SPCI-X Bus

J2F1 Logic analyzer Mictor Connector for 80219 Peripheral Bus

J3F2 Logic analyzer Mictor Connector for 80219 Peripheral Bus

J3F1 General Purpose I/O (GPIO) Header – GPIO 0-2

J1A1 Secondary PCI-X Expansion Slot

J1B1 Secondary PCI-X Expansion Slot – Not Populated

J2H1 Primary PCI/PCI-X Edge Connector

J6G1 DDR DIMM Connector

J8H1 Connector for Battery

Table 33. GPIO Header (J3F1) Definition

Pin Signal Pin Signal

1GPIO04 GND

2GPIO15 GND

3GPIO26 GND