Evaluation Platform Board Manual 39

Intel

®

IQ80332 I/O Processor

Hardware Reference Section

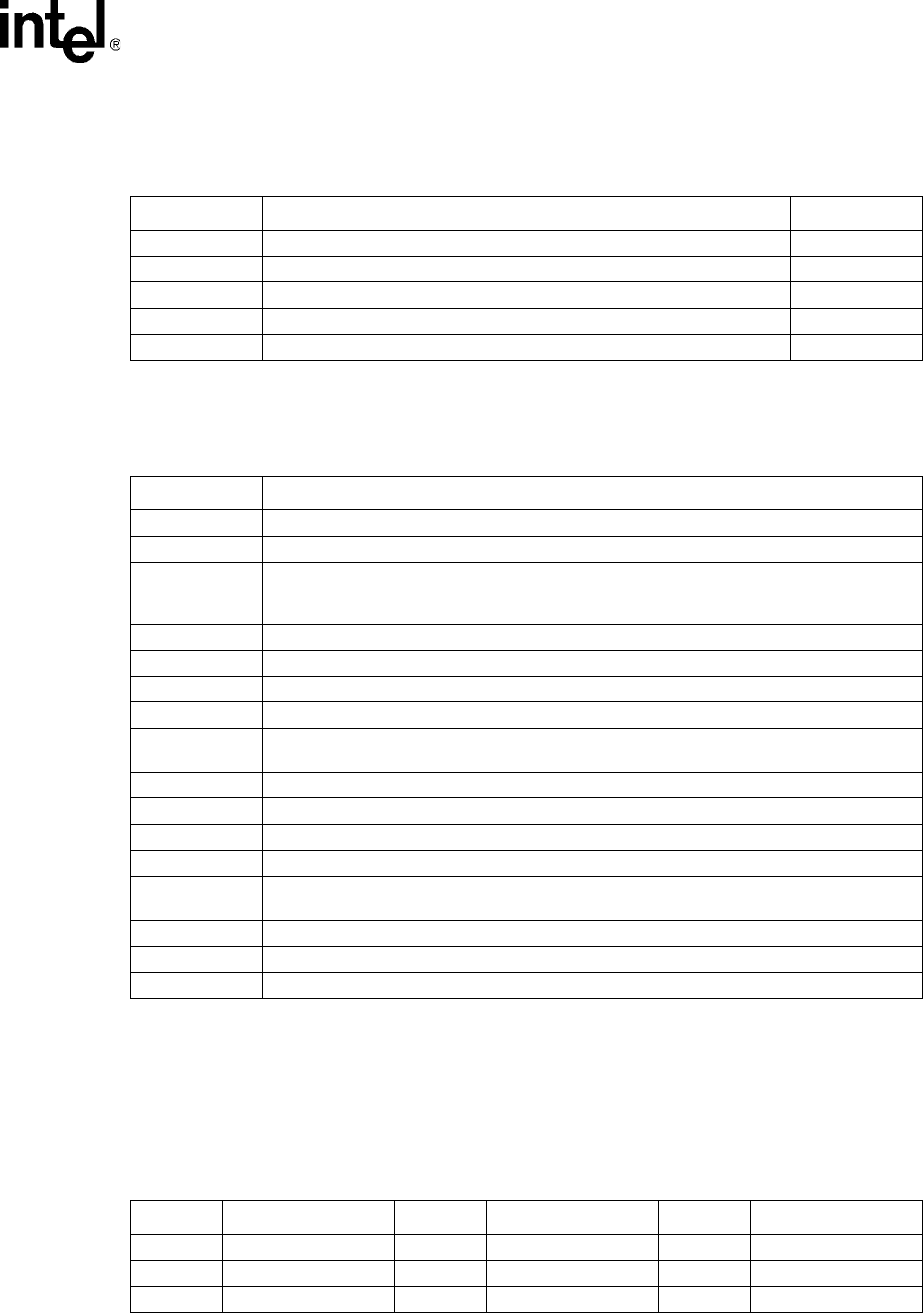

3.9.3 Jumper Summary

3.9.4 Connector Summary

3.9.5 General Purpose Input/Output Header

The following table in Section 19, “J2D2 GPIO Header Definition” on page 39 shows the GPIO

signal assignments. The GPIO signals are muxed with the serial port signals. The serial port must be

disabled to use the GPIO signals. These pins corespond to Jumer J2D2.

Table 17. Jumper Summary

Jumper Description Factory Default

J1C1 JTAG Chain Enable 1-2

J1D2 Disables UART Open

J7B4 SM_SCLK to EEPROM, SM_SDTA to EEPROM 1-2, 3-4

J7D1 16-bit Flash Enable Open

J9D3 Buzzer Volume Open

Table 18. Connector Summary

Connector Description

J1D1 RJ45 Network Connector for GbE NIC.

J1E1 RJ11 Dual Serial Port Connector.

J1L1, J1M1,

J1M2, J1N1,

J2M1, J2M2

SMA connectors

J1R1 Secondary PCI-X Expansion bus Slot

J2A1 Secondary PCI-X Expansion bus Slot.

J2D1 Power header for fan.

J2D2 GPIO tap-in Header

J1B1, J5D1,

J5C1

Test headers

J2E1 Edge connector for primary PCI Express Bus.

J5B1 DIMM

J7A1 PC104 Mod connector.

J7B1, J7B2 I

2

C 4 pin connectors.

J7B3

Secondary PCI-X Expansion Slot Power. Please see Section 2.2.2, “Power Requirements”

for more details

J7C1 Test header (empty)

J7D2 JTAG CPLD Header.

J9D1 Power header for battery.

Table 19. J2D2 GPIO Header Definition

Pin Signal Pin Signal Pin Signal

1 GND 4GPIO57GPIO2

2GPIO75GPIO48GPIO1

3GPIO66GPIO39GPIO0