Intel Core 2 Duo Processor and Intel Q35 Express Chipset—Setting Up and Configuring the

Development Kit

Intel

®

Core

TM

2 Duo Processor and Intel

®

Q35 Express Chipset Development Kit

User’s Manual October 2007

32 Order Number: 318476001US

3.5 Post Codes Definitions

The CRB BIOS writes progress and error codes to Port 80 during POST. These codes are

defined below.

3.5.1 Normal Post Codes

Uncompressed INIT code checkpoints

Before D1 – Early chipset and SIO initialization. NMI disabled.

D1 Perform keyboard controller BAT test. Save power-on CPUID to

scratch CMOS.

D0 Go to flat mode with 4GB limit. Start checksum verification.

D2 Disable cache and begin sizing full memory array.

D3 Additional chipset initialization, re-enable cache.

D4 Test base 512 MB of memory, adjust policies and cache first 8

MB.

D5 Bootblock code copied from ROM to lower system memory. BIOS

now executes out of RAM.

D6 Check for recovery mode and verify main BIOS checksum.

If either in recovery mode or main BIOS checksum is bad, go to check point E0

else goto checkpoint D7.

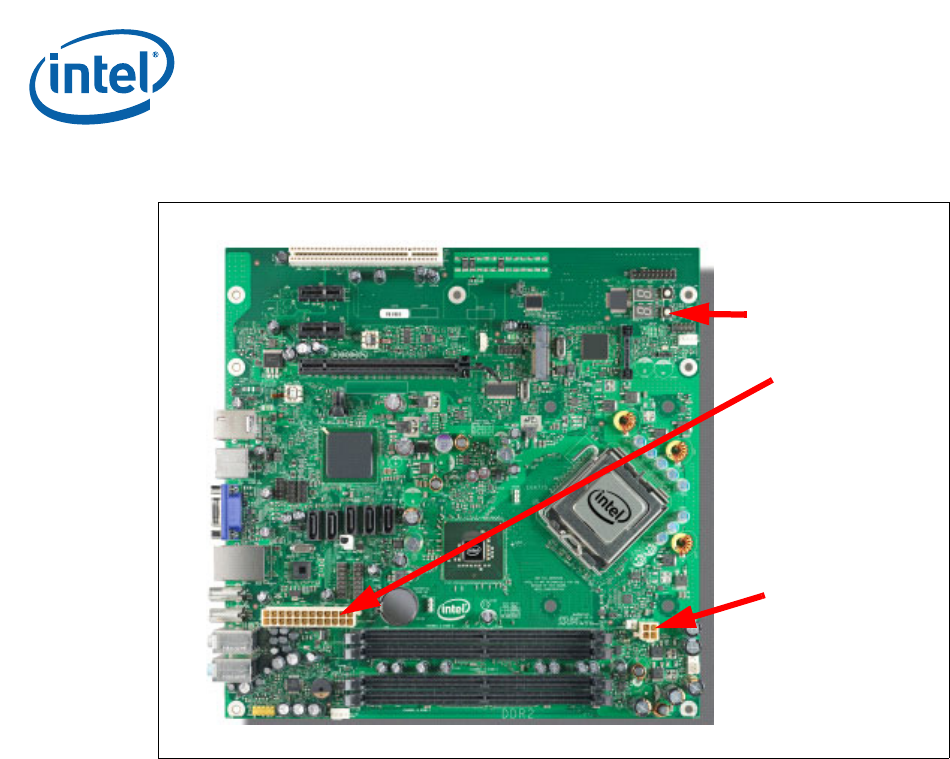

Figure 24. 2x12 Standard power supply and 2x2 power supply

Power-on button

2x12 Standard

power supply

2x2 Standard

power supply