High Availability Software for the Intel

®

NetStructure

TM

ZT 4901 Technical Product Specification 17

Introduction

2.2.3 Backplane

The RSS system backplane supports two CompactPCI buses accessible by both Redundant Hosts.

In Active-Standby mode, the active processor board controls the buses (Active Host) and the

standby processor board is isolated from the backplane (Drone mode). By using Active-Active-

capable processor boards such as the ZT 5524, the system can be configured so that each processor

board has access to one backplane bus (Cluster mode). The backplane has separate buses for

active-to-standby processor board communication (COMM) and Host Controller functions. See

Figure 4, “High-Availability System Backplane Architecture” on page 18 for an example of a

typical High-Availability backplane.

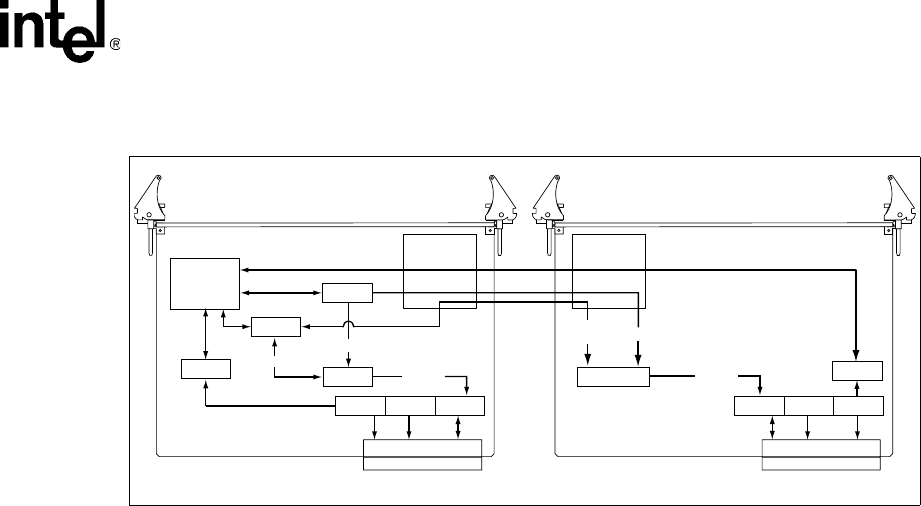

Figure 3. RSS Host with Bridge Mezzanine Block Diagram

Base CPU Board

CPU/

Chipset

xMC

HC

PCI

CIC

Iso/Term Clk. Arb.

Control

Control/Status

Control/

Status

CompactPCI J1/J2

Bus Segment A

Interboard

Connector

Interboard

Connector

Xreq

Bridge Mezzanine

PCI

CIC

Iso/TermClk.Arb.

Control

CompactPCI J1/J2

Bus Segment B

Xreq