Chapter 4 Analog Input

NI 6232/6233 User Manual 4-24 ni.com

A counter on your device internally generates ai/SampleClock unless you

select some external source. ai/StartTrigger starts this counter and either

software or hardware can stop it when a finite acquisition completes. When

using an internally generated ai/SampleClock, you also can specify a

configurable delay from ai/StartTrigger to the first ai/SampleClock pulse.

By default, this delay is set to two ticks of the ai/SampleClockTimebase

signal. When using an externally generated ai/SampleClock, you must

ensure the clock signal is consistent with respect to the timing requirements

of ai/ConvertClock. Failure to do so may result in ai/SampleClock pulses

that are masked off and acquisitions with erratic sampling intervals. Refer

to the AI Convert Clock Signal section for more information on the timing

requirements between ai/ConvertClock and ai/SampleClock.

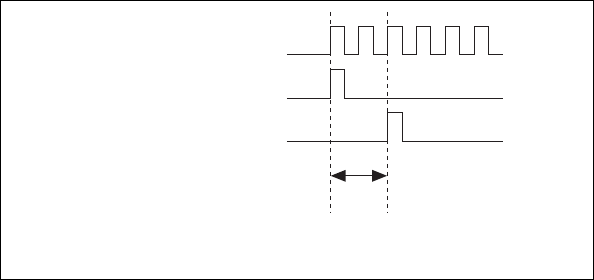

Figure 4-11 shows the relationship of ai/SampleClock to ai/StartTrigger.

Figure 4-11. ai/SampleClock and ai/StartTrigger

AI Sample Clock Timebase Signal

You can route any of the following signals to be the AI Sample Clock

Timebase (ai/SampleClockTimebase) signal:

• 20 MHz Timebase

• 100 kHz Timebase

•PXI_CLK10

•RTSI <0..7>

• Input PFI <0..5>

•PXI_STAR

ai/SampleClockTimebase is not available as an output on the I/O connector.

ai/SampleClockTimebase is divided down to provide one of the possible

ai/SampleClockTimebase

ai/StartTrigger

ai/SampleClock

Delay

From

Start

Trigger