1998 Feb 16 29

Philips Semiconductors Product specification

CMOS digital decoding IC with RAM for

Compact Disc

SAA7345

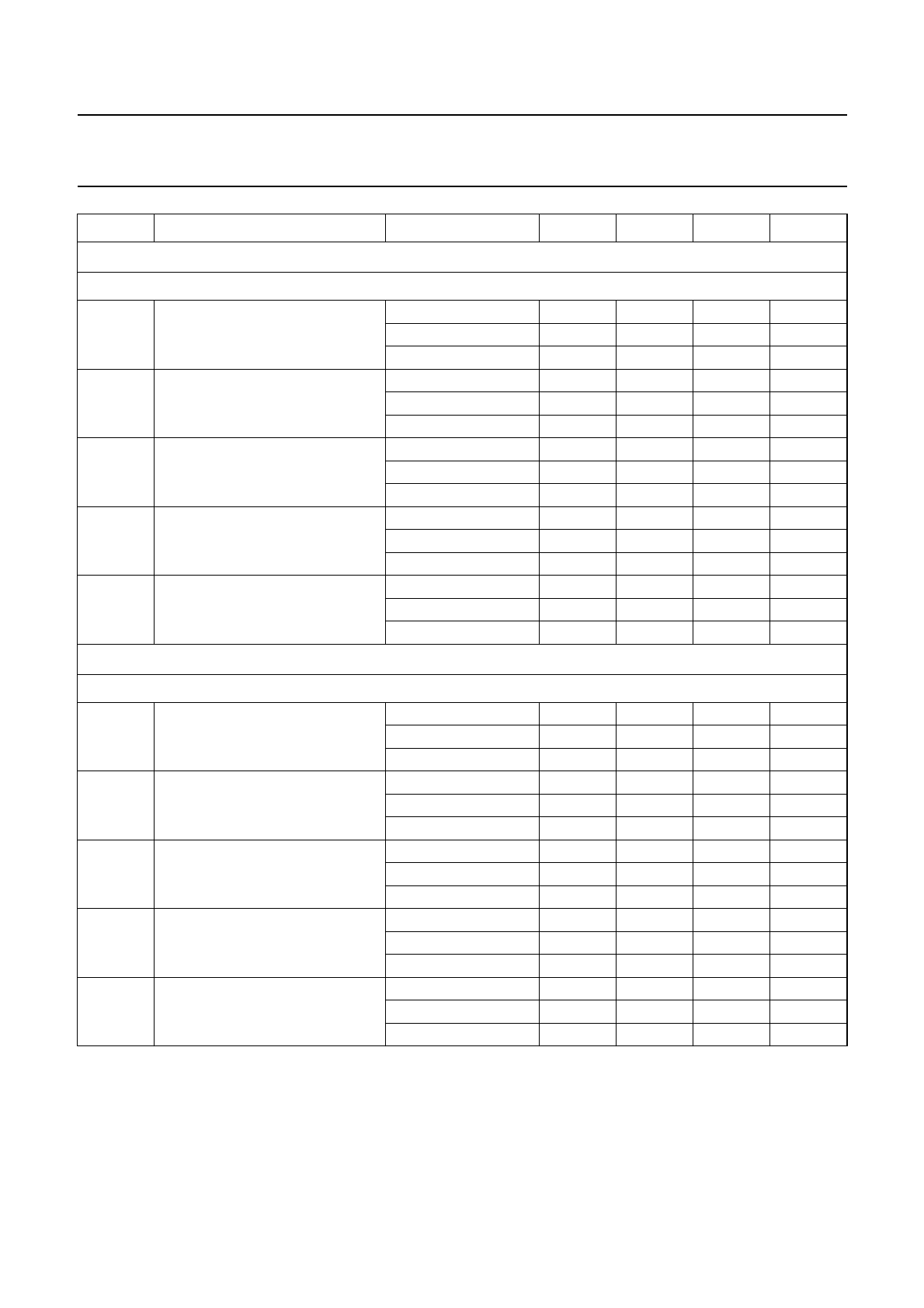

I

2

S timing

CLOCK OUTPUT SCLK (see Fig.23)

t

cy

output clock period sample rate = f

s

− 472.4 − ns

sample rate = 2f

s

− 236.2 − ns

sample rate = 4f

s

− 118.1 − ns

t

H

clock HIGH time sample rate = f

s

166 −−ns

sample rate = 2f

s

83 −−ns

sample rate = 4f

s

42 −−ns

t

L

clock LOW time sample rate = f

s

166 −−ns

sample rate = 2f

s

83 −−ns

sample rate = 4f

s

42 −−ns

t

su

set-up time sample rate = f

s

95 −−ns

sample rate = 2f

s

48 −−ns

sample rate = 4f

s

24 −−ns

t

h

hold time sample rate = f

s

95 −−ns

sample rate = 2f

s

48 −−ns

sample rate = 4f

s

24 −−ns

I

2

S timing (double speed)

CLOCK OUTPUT SCLK (see Fig.23)

t

cy

output clock period sample rate = f

s

− 236.2 − ns

sample rate = 2f

s

− 118.1 − ns

sample rate = 4f

s

− 59.1 − ns

t

H

clock HIGH time sample rate = f

s

83 −−ns

sample rate = 2f

s

42 −−ns

sample rate = 4f

s

21 −−ns

t

L

clock LOW time sample rate = f

s

83 −−ns

sample rate = 2f

s

42 −−ns

sample rate = 4f

s

21 −−ns

t

su

set-up time sample rate = f

s

48 −−ns

sample rate = 2f

s

24 −−ns

sample rate = 4f

s

12 −−ns

t

h

hold time sample rate = f

s

48 −−ns

sample rate = 2f

s

24 −−ns

sample rate = 4f

s

12 −−ns

SYMBOL PARAMETER CONDITIONS MIN. TYP. MAX. UNIT