( 49 / 68 )

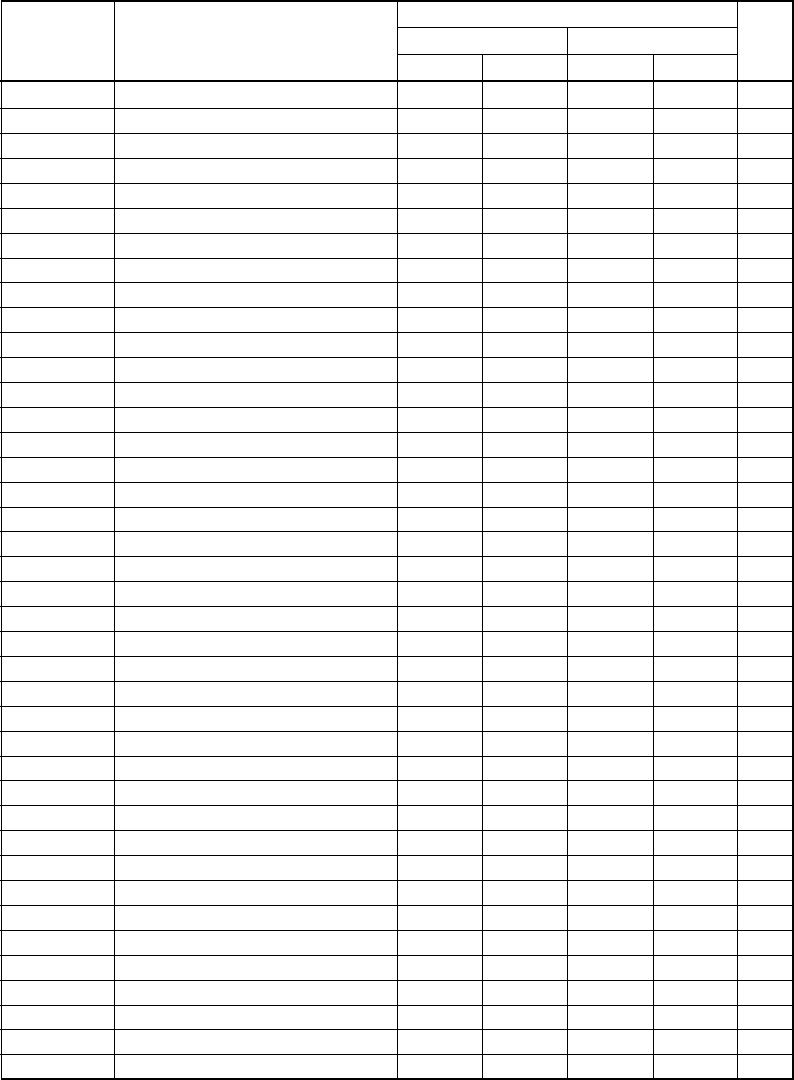

5.3 Operation Timing

With this emulator system, ports P0 to P3 and P40 are connected via the emulation circuit. Therefore,

I/O timing will differ from that of the actual MCU. Use the following as a reference when using the

emulation pod.

(1) Operation Timing When Using the Evaluation MCU (M37641M8-XXXFS)

Table 5.2 Timing requirements and switching characteristics (Vcc = 5.0V, Ø = 12 MHz)

td (ø-AH) AB15 - AB8 delay time 31 32 ns

tv (ø-AH) AB15 - AB8 valid time 5 0 ns

td (ø-AL) AB7 - AB0 delay time 33 33 ns

tv (ø-AL) AB7 - AB0 valid time 5 0 ns

td (ø-WR) WR* delay time 6 15 ns

tv (ø-WR) WR* valid time 3 3 ns

td (ø-RD) RD* delay time 6 15 ns

tv (ø-RD) RD* valid time 3 3 ns

td (ø-DMA) DMAOUT delay time 25 25 ns

tv (ø-DMA) DMAOUT valid time 5 0 ns

tsu (RDY-ø) RDY setup time 21 45 ns

th (ø-RDY) RDY hold time 0 0 ns

tsu (HOLD-ø) HOLD* setup time 21 34 ns

th (ø-HOLD) HOLD* hold time 0 0 ns

td (ø-HLDAL) HLDA* "L" delay time 25 25 ns

td (ø-HLDAH) HLDA* "H" delay time 25 25 ns

tsu (DB-ø) Data bus setup time 7 38 ns

th (ø-DB) Data bus hold time 0 0 ns

td (ø-DB) Data bus delay time 22 23 ns

tv (ø-DB) Data bus valid time 13 8 ns

td (ø-EDMA) EDMA* delay time 9 16 ns

tv (ø-EDMA) EDMA* valid time 4 0 ns

td (AH-WR) Before WR* AB15 - AB8 valid time 0.5*tc(ø)-28 0.5*tc(ø)-33 ns

td (AL-WR) Before WR* AB7 - AB0 valid time 0.5*tc(ø)-30 0.5*tc(ø)-35 ns

tv (WR-AH) After WR* AB15 - AB8 valid time 0 -5 ns

tv (WR-AL) After WR* AB7 - AB0 valid time 0 -5 ns

td (AH-RD) Before RD* AB15 - AB8 valid time 0.5*tc(ø)-28 0.5*tc(ø)-33 ns

td (AL-RD) Before RD* AB7 - AB0 valid time 0.5*tc(ø)-30 0.5*tc(ø)-35 ns

tv (RD-AH) After RD* AB15 - AB8 valid time 0 -5 ns

tv (RD-AL) After RD* AB7 - AB0 valid time 0 -5 ns

tsu (RDY-WR) Before WR* RDY setup time 27 47 ns

th (WR-RDY) After WR* RDY hold time 0 0 ns

tsu (RDY-RD) Before RD* RDY setup time 27 47 ns

th (RD-RDY) After RD* RDY hold time 0 0 ns

tsu (DB-RD) Before RD* data bus setup time 13 40 ns

th (RD-DB) After RD* data bus hold time 0 0 ns

td (WR-DB) Before WR* data bus delay time 20 25 ns

tv (WR-DB) After WR* data bus valid time 10 3 ns

tv (WR-EDMA) After WR* EDMA* delay time 2 2 ns

tv (RD-EDMA) After RD* EDMA* delay time 2 2 ns

Min.

Max. Min. Max.

Actual MCU Emulator

Symbol Item Unit

Standard value