( 50 / 68 )

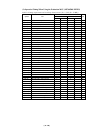

Table 5.3 Timing requirements and switching characteristics (Vcc = 3.0 V, Ø = 6 MHz)

td (ø-AH) AB15 - AB8 delay time 45 51 ns

tv (ø-AH) AB15 - AB8 valid time 7 3 ns

td (ø-AL) AB7 - AB0 delay time 47 52 ns

tv (ø-AL) AB7 - AB0 valid time 7 3 ns

td (ø-WR) WR* delay time 8 15 ns

tv (ø-WR) WR* valid time 4 4 ns

td (ø-RD) RD* delay time 8 15 ns

tv (ø-RD) RD* valid time 3 3 ns

td (ø-DMA) DMAOUT delay time 26 32 ns

tv (ø-DMA) DMAOUT valid time 9 5 ns

tsu (RDY-ø) RDY setup time 35 68 ns

th (ø-RDY) RDY hold time 0 0 ns

tsu (HOLD-ø) HOLD* setup time 21 34 ns

th (ø-HOLD) HOLD* hold time 0 0 ns

td (ø-HLDAL) HLDA* "L" delay time 30 30 ns

td (ø-HLDAH) HLDA* "H" delay time 30 30 ns

tsu (DB-ø) Data bus setup time 9 49 ns

th (ø-DB) Data bus hold time 0 0 ns

td (ø-DB) Data bus delay time 30 36 ns

tv (ø-DB) Data bus valid time 15 8 ns

td (ø-EDMA) EDMA* delay time 12 29 ns

tv (ø-EDMA) EDMA* valid time 8 7 ns

td (AH-WR) Before WR* AB15 - AB8 valid time 0.5*tc(ø)-33 0.5*tc(ø)-34 ns

td (AL-WR) Before WR* AB7 - AB0 valid time 0.5*tc(ø)-35 0.5*tc(ø)-35 ns

tv (WR-AH) After WR* AB15 - AB8 valid time 0 -5 ns

tv (WR-AL) After WR* AB7 - AB0 valid time 0 -5 ns

td (AH-RD) Before RD* AB15 - AB8 valid time 0.5*tc(ø)-33 0.5*tc(ø)-41 ns

td (AL-RD) Before RD* AB7 - AB0 valid time 0.5*tc(ø)-35 0.5*tc(ø)-43 ns

tv (RD-AH) After RD* AB15 - AB8 valid time 0 -5 ns

tv (RD-AL) After RD* AB7 - AB0 valid time 0 -5 ns

tsu (RDY-WR) Before WR* RDY setup time 45 83 ns

th (WR-RDY) After WR* RDY hold time 0 0 ns

tsu (RDY-RD) Before RD* RDY setup time 45 76 ns

th (RD-RDY) After RD* RDY hold time 0 0 ns

tsu (DB-RD) Before RD* data bus setup time 18 56 ns

th (RD-DB) After RD* data bus hold time 0 0 ns

td (WR-DB) Before WR* data bus delay time 28 29 ns

tv (WR-DB) After WR* data bus valid time 12 3 ns

tv (WR-EDMA) After WR* EDMA* delay time 3 3 ns

tv (RD-EDMA) After RD* EDMA* delay time 3 3 ns

Min.

Max. Min. Max.

Actual MCU Emulator

Symbol Item Unit

Standard value