BIOS Setup Utility

SY-P4X400 DRAGON Lite

58

3-4.2 CPU & PCI Bus Control

Caution:

Change these settings only if you are already familiar

with the Chipset.

The [CPU & PCI Bus Control] option changes the values of the chipset

registers. These registers control the system options in the computer.

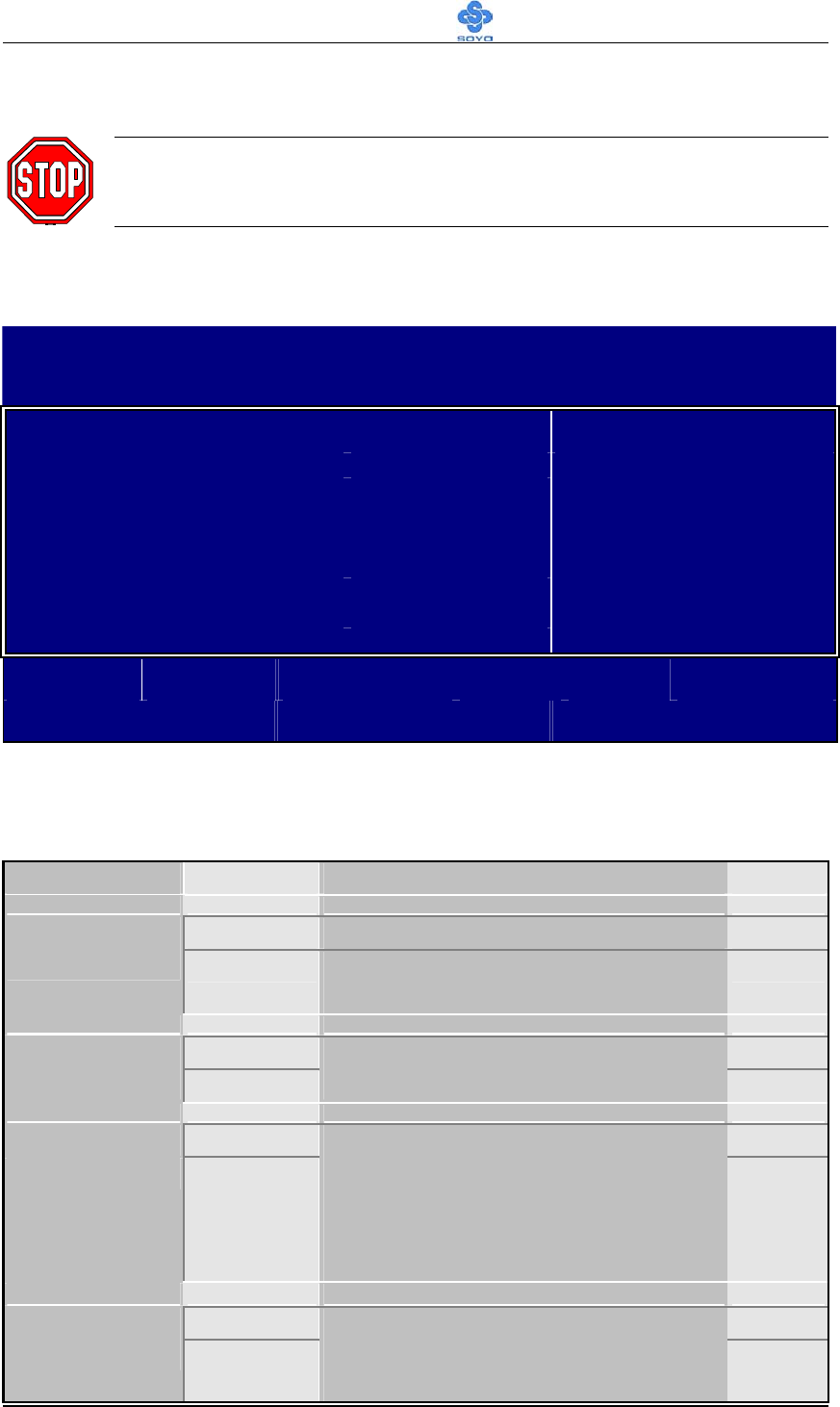

CMOS Setup Utility – Copyright ( C ) 1984-2002 Award Software

CPU & PCI Bus Control

CPU to PCI Write Buffer Enabled

Item Help

PCI Master 0 WS Write Enabled

PCI Delay Transaction Disabled

VLink 8X Support Enabled

Menu Level

:Move

Enter:Select +/-/PU/PD:Value F10:Save ESC:Exit F1:General Help

F5:Previous Values F6:Fail-Safe Defaults F7: Optimized Defaults

After you have completed the changes, press [Esc] and follow the

instructions on your screen to save your settings or exit without saving.

CPU & PCI Bus Control

Setting Description Note

Disabled

CPU to PCI

Write Buffer

Enabled Enabled the CPU to PCI Write

Buffer.

Default

Disabled

PCI Master 0

WS Write

Enabled

This item allows you to

enabled/disabled the PCI post write.

Default

PCI Delay

Disabled Default

Transaction

Enabled

The chipset has an embedded 32-bit

posted write buffer to support delay

transactions cycles. Select

Enabled

to support compliance with PCI

specification version 2.1.

Disabled

VLink 8X

Support

Enabled

Enabled item can support Quad Data

Transfer interconnect to the VT8235

South Bridge.

Default