Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

Revision 1.22 (09-25-08) 104 SMSC LAN9420/LAN9420i

DATASHEET

4.3.1 Bus Mode Register (BUS_MODE)

This register establishes the bus operating modes for the DMAC.

Offset: 0000h Size: 32 bits

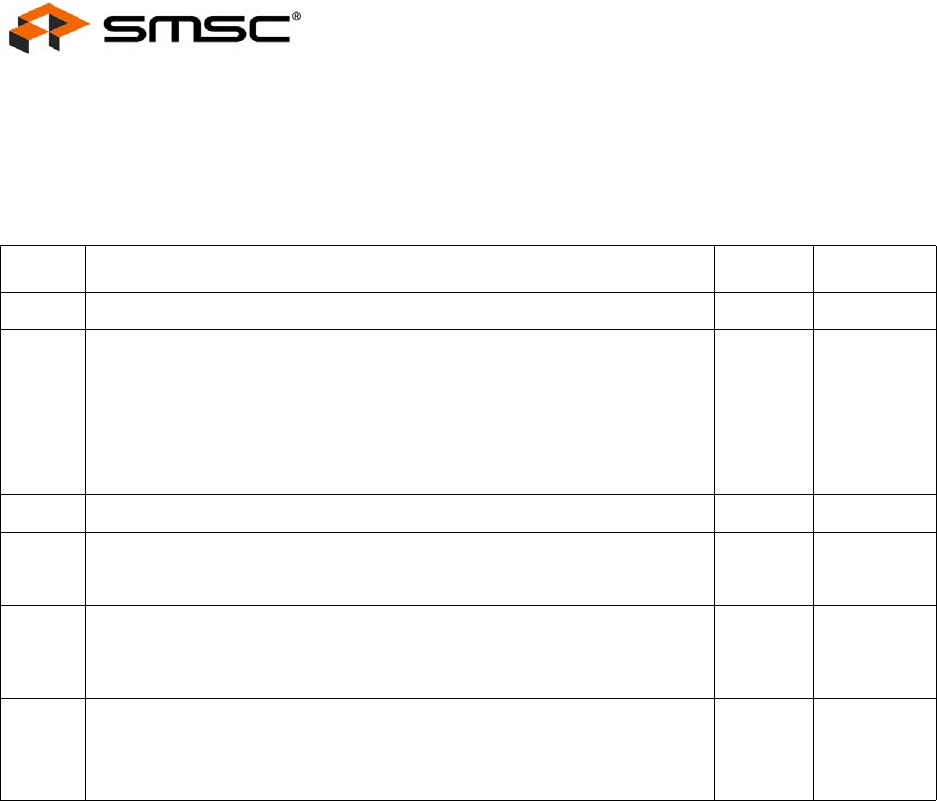

BITS DESCRIPTION TYPE DEFAULT

31:14 RESERVED RO -

13:8 Programmable Burst Length (PBL)

Indicates the maximum number of DWORDs to be transferred in one DMA

transaction. This will be the maximum value that is used in a single block

read/write. The DMAC will always attempt to burst transfer the length

specified in the PBL each time it starts a burst transfer.

PBL can be programmed with permissible values of 1, 2, 4, 8, 16 and 32.

Any other value will result in undefined behavior.

R/W 001000b

7 RESERVED RO -

6:2 Descriptor Skip Length (DSL)

Specifies the number of DWORDs to skip between two unchained

descriptors.

R/W 00000b

1 Bus Arbitration (BAR)

When this bit is set the RX DMA operations are given priority while

guarantying TX at least one grant in between consecutive RX packets.

When cleared, the arbitration ratio is dictated by the BUS_CFG[26:25] field.

R/W 0b

0 Software Reset (SRST)

When this bit is set, the DMAC and MAC are reset. This is a self-clearing

bit.

Note: It will take up to 120ns for the SRST to complete

R/W/SC 0b