Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

SMSC LAN9420/LAN9420i 153 Revision 1.22 (09-25-08)

DATASHEET

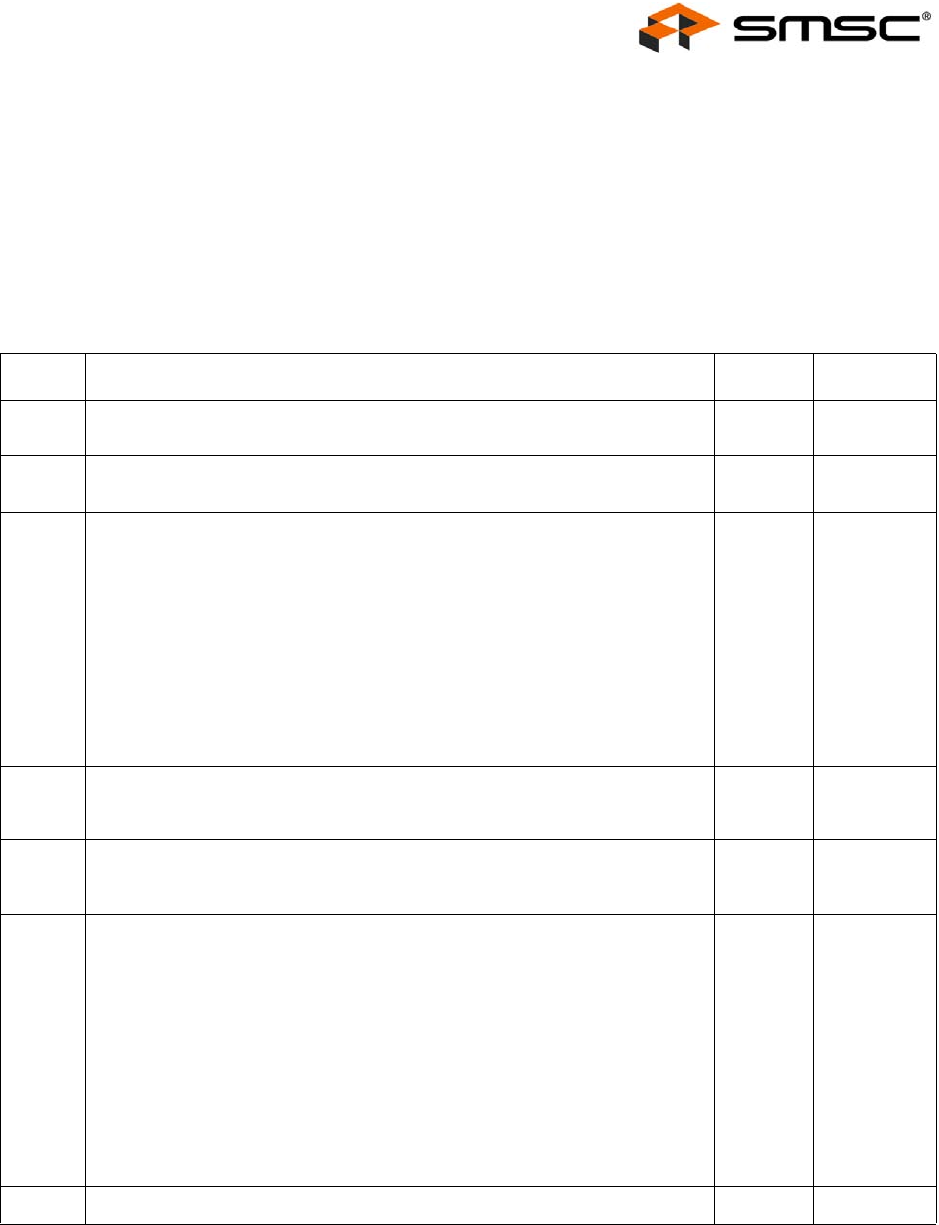

4.6.2 PCI Power Management Control and Status Register (PCI_PMCSR)

This register controls the device’s power state.

Note: The format of this register is equivalent to offsets 7:4 of the Power Management Register Block

Definition as described in Revision 1.1 of the PCI Bus Power Management Interface

Specification.

Offset: 7Ch Size: 32 bits

BITS DESCRIPTION TYPE DEFAULT

31:24 Data (PM_DATA)

This field is not implemented and returns zeros.

RO 00h

23:16 PMCSR PCI to PCI Bridge Support Extensions (PMCSR_BSE)

This field is not implemented and returns zeros.

RO 00h

15 PME Status (PME_STATUS)

This bit is set when an enabled power management event has been

detected. Writing a “1” to this bit will clear it provided that the source of the

event has been cleared. This bit is level-triggered and will not clear on write

if the source of the power management event remains asserted. Writing a

“0” has no effect.

When the VAUXDET input pin is low, this bit is reset on assertion of a power-

on reset or PCI reset (PCInRST).

When the VAUXDET input pin is high, this bit is unaffected by assertion of

PCI reset (PCInRST). In this case, the bit will maintain its setting until

cleared with a write, or until assertion of a power-on reset.

R/WC Note 4.11

14:13 Data Scale (DATA_SCALE)

This field is not implemented and returns zeros as a result of the PM_DATA

field of this register not being implemented.

RO 00b

12:9 Data Select (DATA_SELECT)

This field is not implemented and returns zeros as a result of the PM_DATA

field of this register not being implemented.

RO 0000b

8 PME Enable (PME_EN)

When this bit is set, the device will assert the external nPME signal if the

PME Status (PME_STATUS) bit in this register is set. When this bit is

cleared, the device will not assert the external nPME signal.

When the VAUXDET input pin is cleared, this bit is reset on assertion of a

power-on reset or PCI reset (PCInRST).

When the VAUXDET input pin is set, this bit is unaffected by assertion of

PCI reset (PCInRST). In this case, the bit will maintain its setting until

cleared with a write, or until assertion of a power-on reset.

If PME_EN is cleared, the device will automatically place the PHY into

General Power-Down when entering the D3

HOT

state.

R/W Note 4.11

7:2 RESERVED RO -