Single-Chip Ethernet Controller with HP Auto-MDIX Support and PCI Interface

Datasheet

SMSC LAN9420/LAN9420i 149 Revision 1.22 (09-25-08)

DATASHEET

4.6 PCI Configuration Space CSR (CONFIG CSR)

Configuration and read back of the CONFIG CSR is accomplished by the Host processor via the PCI

bus. These registers assume their default value on assertion of a chip-level reset or when the device

power state transitions from D3 to D0. See Section 3.7, "Power Management," on page 73 for details.

Registers in offsets 00h - 03Fh are standard PCI header registers, as described in the PCI Local Bus

Specification Revision 3.0. Please refer to the specification for further details.

Register 78h is a PCIB specific extension related to power management.

The following is the register map for the PCI Configuration Space CSR (CONFIG CSR):

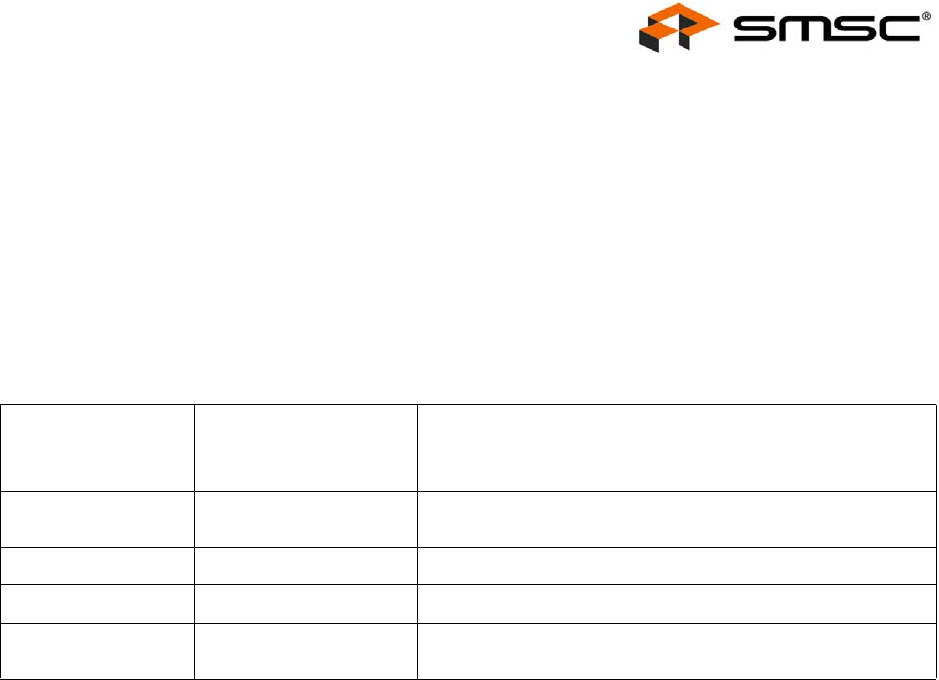

Table 4.9 PCI Configuration Space CSR (CONFIG CSR) Address Map

CONFIGURATION

SPACE

OFFSET REGISTER NAME DESCRIPTION

00h – 3Fh - Standard PCI Header Registers (See Table 4.10 on page 150

for details).

40h – 74h RESERVED

78h PCI_PMC PCI Power Management Capabilities Register (PCI_PMC)

7Ch PCI_PMCSR PCI Power Management Control and Status Register

(PCI_PMCSR)