Thales Computers 2-3 CPMC-1553R User’s Guide, CA.DT.356-0e

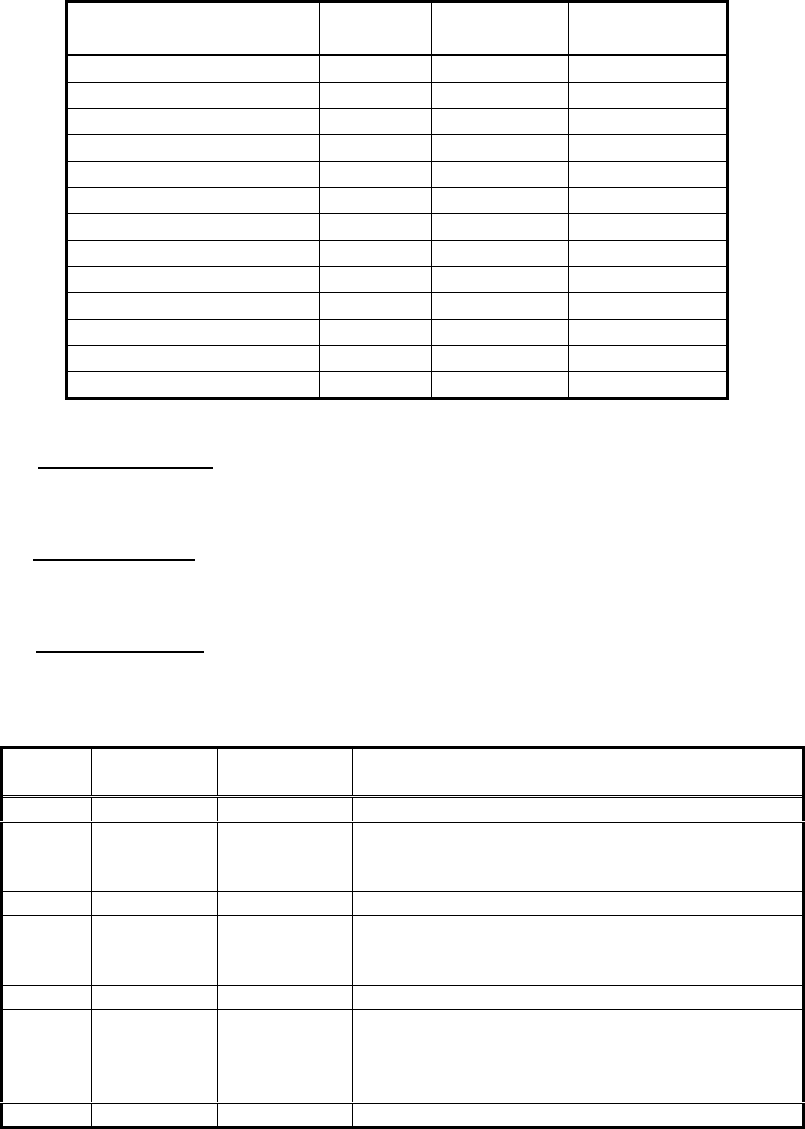

Table 3. Summary of Implemented PCI Configuration Registers

Register Name

Address

(0x)

Read/Write

Default Value

(0x)

Vendor ID 00 Read 151E

Device ID 02 Read 0001

Command Register 04 Read/Write 0000

Status Register 06 Read/Write 0400

Revision ID 08 Read 03 or higher

Class Code 09 Read 078000

Header Type 0E Read 00

Base Address Register 0 10 Read/Write FFFC0000

Base Address Register 1 14 Read/Write FFFFF000

Subsystem Vendor ID 2C Read 151E

Subsystem ID 2E Read 0001

Interrupt Line 3C Read/Write 00

Interrupt Pin 3D Read 01

2.2.1.1 Vendor ID Register The Vendor ID is a 16-bit register assigned to Thales Computers that

identifies the manufacturer of the device. The value of this register should always be 0x151E.

2.2.1.2 Device ID Register The Device ID is a 16-bit read-only register assigned by Cetia that identifies

the PCI interface device. The value of this register should always be 0x0001.

2.2.1.3 Command Register The Command Register is a 16-bit read/write register that provides basic

control over the ability of the CPMC-1553R board to respond to the PCI bus. The Command Register is

defined in Table 4. The default value of the Command Register is 0x0000.

Table 4. Command Register Definition

Data

Bit

Mnemonic Read/Write Definition

0 IO_ENA Read/Write Read/write to I/O access enable.

1 MEM_ENA Read/Write Memory Access Enable. When high, MEM_ENA

allows the CPMC-1553R to respond to PCI Bus

memory accesses.

5..2 Unused — —

6 PERR_ENA Read/Write Parity Error Enable. When high, PERR_ENA

enables the CPMC-1553R to report parity errors via

the PERR* output.

7Unused — —

8 SERR_ENA Read/Write System Error Enable. When high, SERR_ENA

allows the CPMC-1553R to report address parity

errors via the SERR* output. However, to signal a

system error, the PERR_ENA bit must also be high.

15..9 Unused — —