Thales Computers 2-4 CPMC-1553R User’s Guide, CA.DT.356-0e

2.2.1.4 Status Register The Status Register is a 16-bit read/write register that provides the status of bus-

related events. Read transactions tell you the current status of the bits. The Status Register is cleared by

writing a logic one to that bit. Writing a logic zero has no affect on the registers. The status register is

defined in Table 5. The default value of the status register is 0x0400.

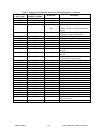

Table 5. Status Register Definition

Data Bit Mnemonic Read/Write Definition

8..0 Unused

——

10..9 DEVSEL_TIM Read Device Select Timing. The DEVSEL_TIM bits

indicate target access timing of the CPMC-1553R

board function. This board function is designed to be

a slow target device. These bits are always read as

0x10b.

11 TABORT_SIG Read/Write Target Abort Signaled. This bit is set when a local

peripheral device terminates a transaction. The

CPMC-1553R board automatically sets this bit if it

issued a target abort after the local side asserted

LT_ABORT*. This bit is driven to the local side on

the TABORT_SIG output.

12 TAR_ABRT_REC Read/Write Target Abort. When high, TAR_ABRT_REC

indicates that the current target device transaction has

been terminated.

13 Unused

——

14 SERR_SET Read/Write Signaled System Error. When high, SERR_SET

indicates that the CPMC-1553R board drove the

SERR* output active (result of address phase parity

error). This signal is driven to the local side on the

SERR_SIG output

15 DET_PAR_ERR Read/Write Detected Parity Error. When high, DET_PAR_ERR

indicates that the CPMC-1553R board detected either

an address or data parity error. Even if parity error

reporting is disabled (PERR_ENA), the CPMC-1553R

board sets the DET_PAR_ERR bit. This signal is

driven to the local side on the PERR_DET output.

2.2.1.5 Revision ID Register The Revision ID register is an 8-bit, read-only register that identifies the

revision number of the device. The value of this register is set by Thales Computers. The current version

should be 0x03 or higher.

2.2.1.6 Class Code Register The Class Code register is a 24-bit, read-only register divided into three

sub-registers: base class, sub-class, and programming interface. The class code register always returns a

value of 0x078000 when read.

2.2.1.7 Cache Line Size Register The Cache Line Size register is not supported.