Thales Computers 2-2 CPMC-1553R User’s Guide, CA.DT.356-0e

2.2 PCI Bus Interface

An Altera FLEX10 PLD provides the interface between the PCI Bus and the ILC-DDC Mini-ACE device.

The FLEX10 operates at 33MHz, is powered by 5V or 3.3V, has a 32-bit data path, and is compliant with

the PCI Local Bus Specification, Revision 2.1. The CPMC-1553R is a target on the PCI Bus.

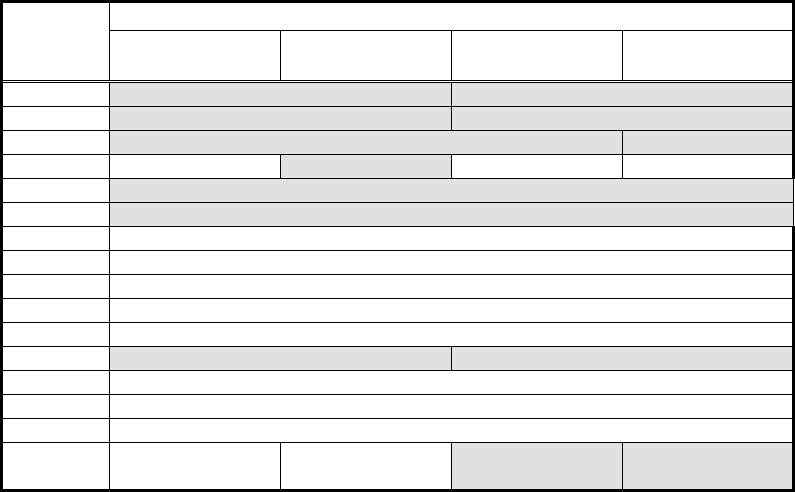

2.2.1 PCI Configuration Space

The PCI configuration space consists of a block of 64 configuration DWORDS, of which, the first 16 are

defined by the PCI Special Interest Group (PCI SIG). The configuration space defined by PCI SIG is

shown in Table 2. The shaded areas indicate registers that are supported by the CPMC-1553R board. A

summary of the supported configuration registers, and their default values is shown in Table 3. Any

registers that are not supported return a value of 0x00 when read.

Table 2. PCI Bus Configuration Registers

Byte

Address

(0x)

3210

00 Device ID Vendor ID

04 Status Register Command Register

08 Class Code Revision ID

0C BIST Header Type Latency Timer Cache Line Size

10 Base Address Register 0

14 Base Address Register 1

18 Base Address Register 2

1C Base Address Register 3

20 Base Address Register 4

24 Base Address Register 5

28 Card Bus CIS Pointer

2C Subsystem ID Subsystem Vendor ID

30 Expansion ROM Base Address Register

34 Reserved

38 Reserved

3C Maximum

Latency

Minimum Grant

Interrupt Pin Interrupt Line