Data 1

HCS

HSTRB

HR/W

HCNTL[1:0]

HD[15:0]

HRDY

HHWIL

Internal

Valid

00

Valid

HPI Operation

www.ti.com

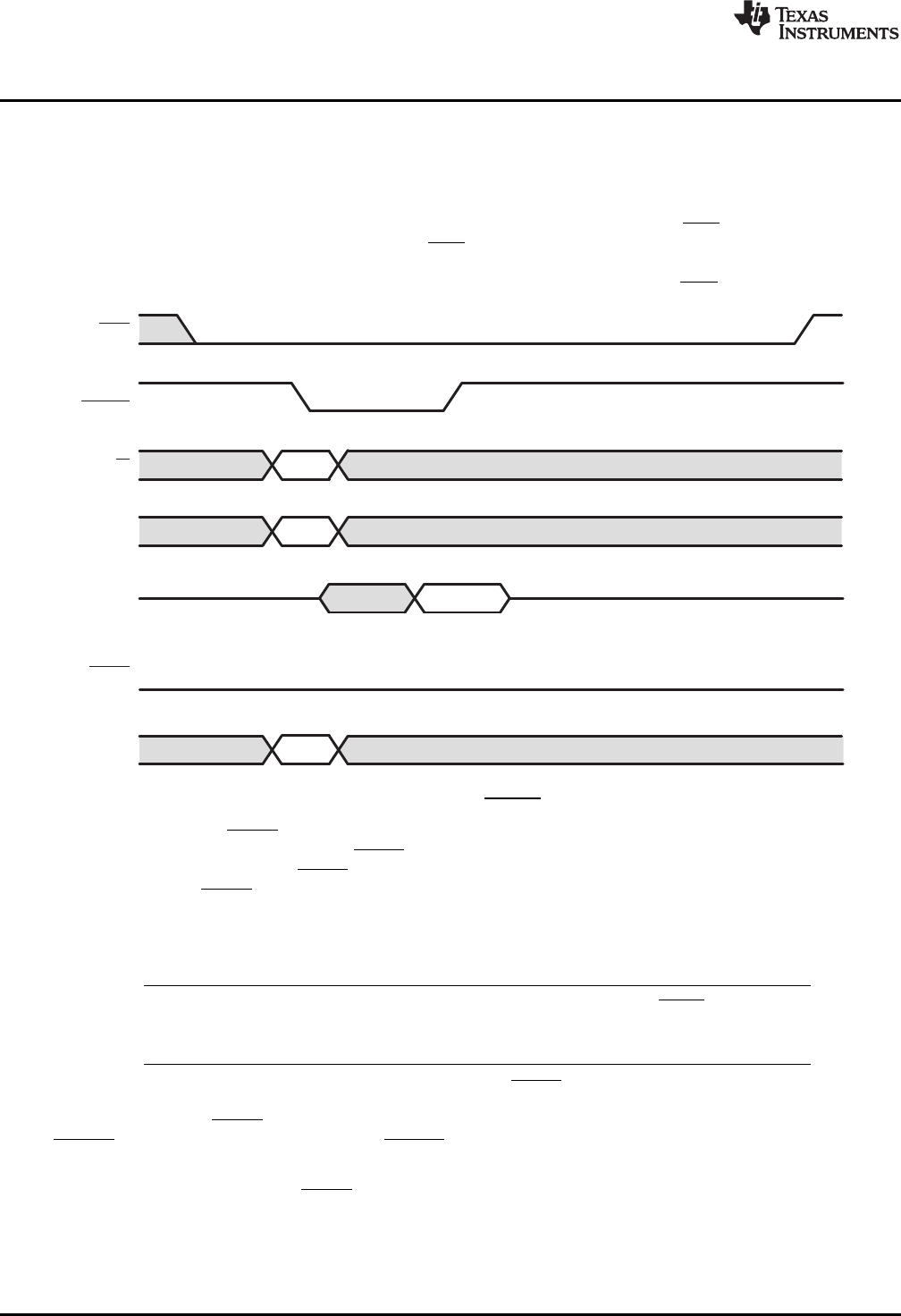

3.8 Single-Halfword HPIC Cycle in the 16-Bit Multiplexed Mode

In 16-bit multiplexed mode, the lower 16 bits of the HPIC registers are duplicated on the upper 16 bits

during HPIC host accesses. Therefore, the host only needs to perform a single halfword cycle access to

read the HPIC register. The host can drive the HHWIL pin either high or low, and either approach returns

the same value. Figure 11 shows the special case in which the host performs a single-halfword cycle to

access the HPIC (see Section 3.5). Although the example in Figure 11 has the HAS signal tied high, this

type of HPIC cycle can also be done using the HAS signal to force early latching of control information.

Figure 11. 16-Bit Multiplexed Mode Single-Halfword HPIC Cycle with HAS Tied High

3.9 Hardware Handshaking Using the HPI-Ready (HRDY) Signal

The HPI ready signal HRDY indicates to the host whether the HPI is ready to complete an access. During

a read cycle, the HPI is ready (drives HRDY low) when it has data available for the host. During a write

cycle, the HPI is ready (drives HRDY low) when it is ready to latch data from the host. If the HPI is not

ready, it can drive HRDY high to insert wait states. These wait states indicate to the host that read data is

not yet valid (read cycle) or that the HPI is not ready to latch write data (write cycle). The number of wait

states that must be inserted by the HPI is dependent upon the state of the accessed resource. See the

device-specific data manual for more information.

NOTE: In some cases, if the host does not have an input pin to connect to the HRDY pin, the host

can check the readiness of the HPI by polling the HRDY bit in the control register (HPIC).

For details, see Section 4.

When the HPI is not ready to complete the current cycle (HRDY high), the host can begin a new host

cycle by forcing the HPI to latch new control information. However, once the cycle has been initiated, the

host must wait until HRDY goes low before causing a rising edge on the internal strobe signal (internal

HSTRB) to complete the cycle. If internal HSTRB goes high when the HPI is not ready, the cycle will be

terminated with invalid data being returned (read cycle) or written (write cycle).

One reason the HPI may drive HRDY high is a not-ready condition in one of its first-in, first-out buffers

(FIFOs). For example, any HPID access that occurs while the write FIFO is full or the read FIFO is empty

may result in some number of wait states being inserted by the HPI. The FIFOs are explained in

Section 6.

22

Host Port Interface (HPI) SPRUGK7A–March 2009–Revised July 2010

Copyright © 2009–2010, Texas Instruments Incorporated