00

HCNTL[1:0]

HD[31:0]

HRDY

HR/W

Internal

HSTRB

HCS

10 11

HPIA Write HPID Write

HRDY

HR/W

Internal

HSTRB

HCS

HCNTL[1:0]

HD[31:0]

www.ti.com

HPI Operation

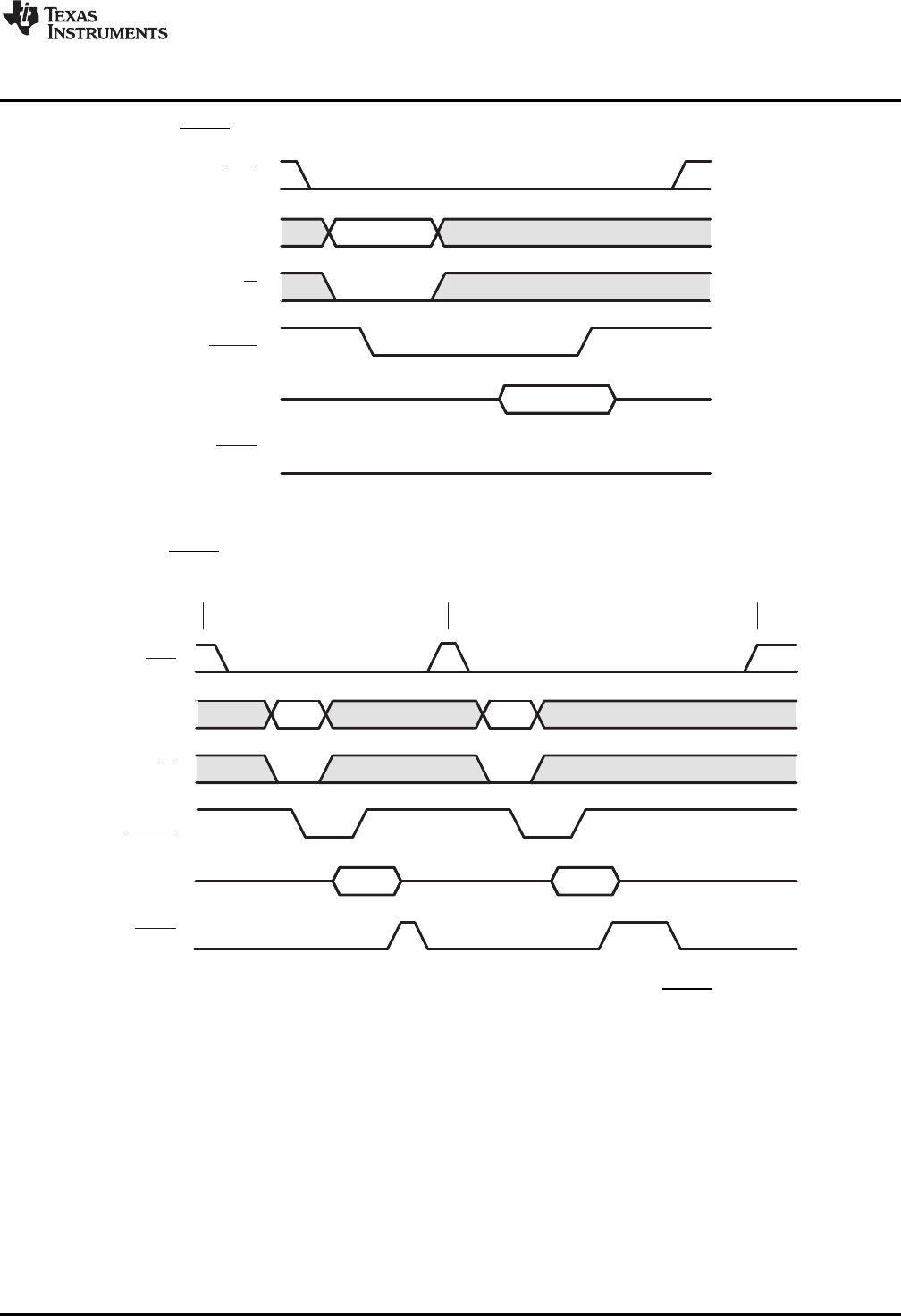

Figure 22. HRDY Behavior During an HPIC Write Cycle in the 32-Bit Multiplexed Mode

Figure 23 shows an HPIA (HCNTL[1:0] = 10b) write access followed by an HPID (HCNTL[1:0] = 11b) write

access for 32-bit multiplexed HPI operation.

Figure 23. HRDY Behavior During a Data Write Operation in the 32-Bit Multiplexed Mode

(Case 1: No Autoincrementing)

Figure 24 shows an HPIA (HCNTL[1:0] = 10b) write access followed by several autoincrementing HPID

(HCNTL[1:0] = 01b) write accesses when the write FIFO is empty. Note that HRDY is active during the

HPIA access but not active during any of the HPID accesses.

27

SPRUGK7A–March 2009–Revised July 2010 Host Port Interface (HPI)

Copyright © 2009–2010, Texas Instruments Incorporated