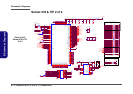

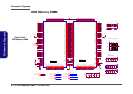

Schematic Diagrams

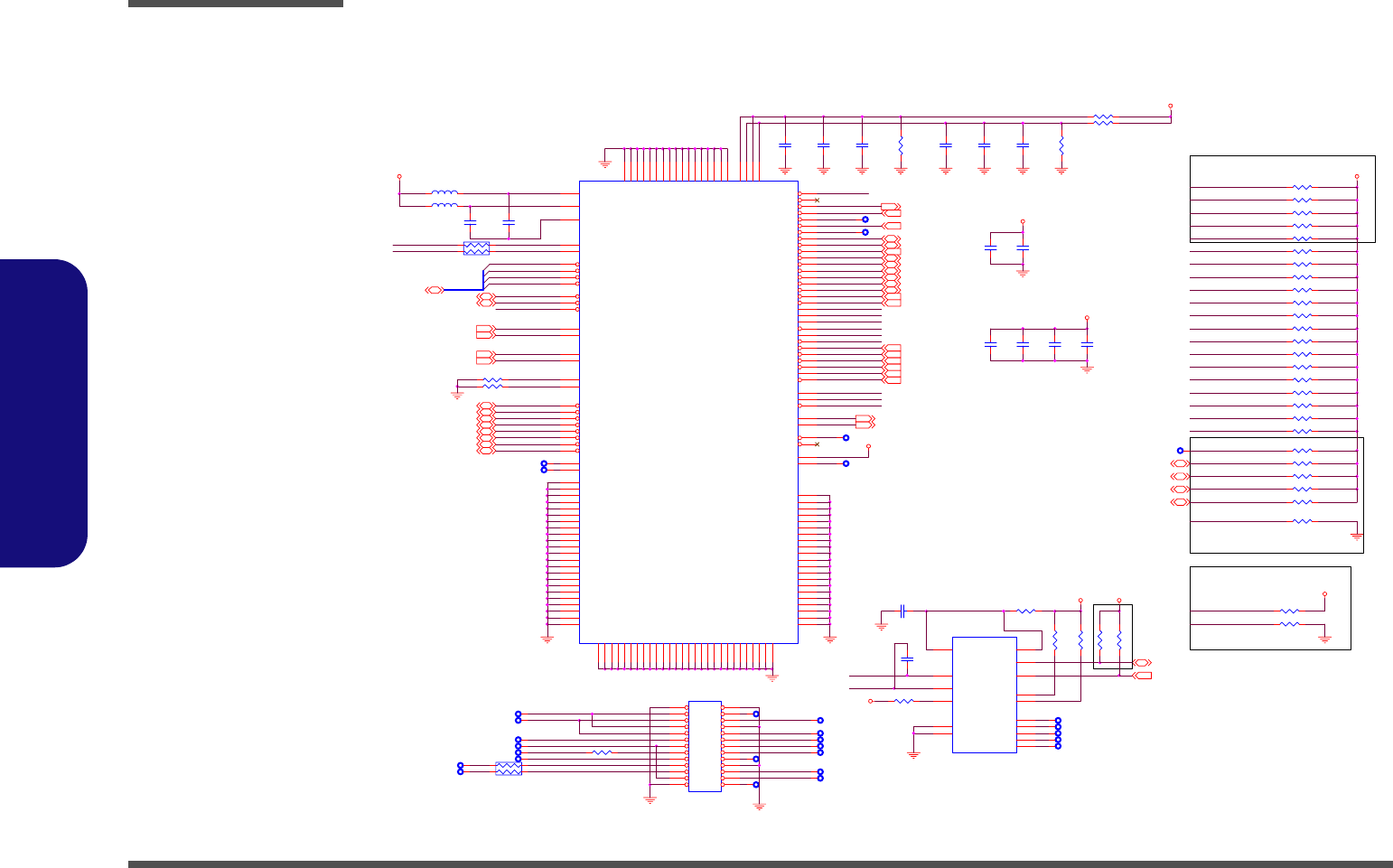

B - 4 Socket 478 & ITP 2 of 2 (71-D4000-D04)

B.Schematic Diagrams

Socket 478 & ITP 2 of 2

VCC_CORE

VCC_CORE

VCC_CORE

VCCVID

+3VS

+3VS VDD3

VCC_CORE

VCC_CORE

VCC_CORE

INTR[15]

NMI[15]

DEFER# [5]

HTRDY# [5]

BPRI# [5]

INIT# [15]

STPCLK# [15]

CPUPWRGD [5]

CPURST# [5]

CPUSLP# [15]

SMI# [15]

IGNNE# [15]

A20M# [15]

FERR# [15]

BNR# [5]

BREQ0# [5]

DBSY# [5]

DRDY# [5]

HLOCK# [5]

HITM# [5]

HIT# [5]

HCLK-CPU#[4]

HCLK-CPU[4]

BSEL0 [4]

BSEL1 [4]

ADS# [5]

HASTB#0[5]

HDSTBN#0[5]

HDSTBN#1[5]

HDSTBN#2[5]

HDSTBN#3[5]

HDSTBP#0[5]

HDSTBP#1[5]

HDSTBP#2[5]

HDSTBP#3[5]

H8_SMDATA[24,33]

H8_SMCLK[24,33]

HASTB#1[5]

DBI#[0..3][5]

HBPM0#[2]

HBPM1#[2]

HBPRM5#[2]

HBPRM4#[2]

CPURST#-T

HCLK_ITP1#

ITP_STPWR

HBPRM4#

HBPM0#

HBPM1#

FERR#

BREQ0#

PROCHOT#

CPUPWRGD

THERMTRIP#

A20M#

STPCLK#

CPUSLP#

SMI#

INIT#

IGNNE#

INTR

NMI

CPURST#

HTDO

IERR

HCLK-CPU

HCLK-CPU#

HTDI-T

HBPRM5#

HBPRM5#-T

HBPM1#-T

HBPRM4#-T

HBPM0#-T

HTDO-T

HTMS-T

HTCK-T

HCLK_ITP1

HTRST#-T

DBRESET-T

HTCK-T

ITP_STPWR-T

SENSE_VCC

DBRESET

HCLK-ITP0

HCLK-ITP0#

HTRST#

HTDI

HTCK

HTMS

HIT#

STPCLK#

HCLK-CPU#

HDSTBP#1

HASTB#0

CPUGTLVREFA

DRDY#

HDSTBN#0

THERMTRIP#

HTRST#

BNR#

BREQ0#

HDSTBP#2

HDSTBN#3

HDSTBP#3

HITM#

HDSTBN#1

HCLK-ITP0#

HTDI

IERR

DBSY#

THERMDC

CPUGTLVREFB

DBI#1

INIT#

CPUPWRGD

A20M#

HDSTBN#2

DBRESET

PROCHOT#

DEFER#

HCLK-CPU

HCLK-ITP0

DBI#2

CPURST#

HTCK

THERMDA

DBI#0

HTDO

DBI#[0..3]

HDSTBP#0

DBI#3

HTRDY#

FERR#

NMI

CPUSLP#

SMI#

IGNNE#

THERMDC

THERMDA

HTMS

BPRI#

HLOCK#

ADS#

INTR

HASTB#1

C387

0.1UF

C302

0.1UF

C301

0.1UF

R298 51

R285

51

R284 51

R274

62_1%

R302

62_1%

R56

51_1%

R293

62_1%

R258 51_1%

R280

75

R327

56_1%

R303 56_1%

R292 56_1%

R270

51_1%

R57 56_1%

R256

56_1%

R273

56_1%

R328 56_1%

R58 56_1%

R244 1.5K

R276

100_1%

R64

100_1%

R63 49.9_1%

R275

49.9_1%

R42

51.1_1%

R243 51.1_1%

R297 10K

RP40 4P2R-0(R)

1

23

4

T

T

T

T

T

T

T

R299 51

JITP1

ITP(R)

1 2

3 4

5 6

7 8

9 10

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

12

34

56

78

910

11 12

13 14

15 16

17 18

19 20

21 22

23 24

25 26

T

T

RP45 4P2R-0(R)

1

2 3

4

R350

0

C80

2200P

U27

EN1617

15

12

14

6

10

1

5

9

13

16

2

3

4

11

7

8

STBY#

SMBDATA

SMBCLK

ADD1

ADD0

NC/CRIT1

NC/CRIT0

NC/OS#

NC

NC

VCC

DXP

DXN

ALERT#

GND

GND

C385 0.1UF

1 2

R317 10K

R316

4.7K

R318

4.7K

R156

2.2K

R157

2.2K

R319 200

T

T

R257 150

R219 51_1%

R218 51_1%

T

T

R306

150

R51 680

R50

27.4_1%

R52

40.2_1%

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

T

JCPU1B

NORTHWOOD478

AC1

V5

A5

AC26

AD26

AE25

L5

R5

P1

E5

D1

F6

F20

AA6

AA21

W23

P23

J23

F21

W22

R22

K22

E22

AF23

AF22

AC3

V6

B6

Y4

AA3

W5

AB2

H5

H2

J6

G1

G4

H6

G2

F3

E3

D2

E2

D4

C1

F7

E6

D5

B3

C4

A2

C3

B2

B5

C6

AB26

AB23

AB25

A4

V21

P26

G25

E21

C25

C5

C7

C9

D10

D12

D14

D16

D18

D20

D21

D24

D3

D6

D8

AE23

AD20

AD22

K24

K3

K6

L1

L23

L26

L4

M2

M22

M25

M5

N21

N24

N3

N6

P2

P22

P25

P5

E13

E15

E17

E19

E23

E26

E4

E7

E9

F10

F12

F14

F16

F18

F2

F22

F25

F5

J2

J22

J25

J5

K21

R1

R23

T6

U2

U22

U25

U5

V1

V23

V26

V4

W21

W24

W3

W6

Y2

Y22

Y25

Y5

G6

R26

E11

E1

F8

G21

G24

T3

T24

T21

G3 R4

AF3

AD6

AD5

L24

AF4

C22

AP0

AP1

VCC_SENSE

ITP_CLK0

ITP_CLK1

DBRESET

ADSTB0

ADSTB1

COMP1

LINT1

LINT0

GTLREF3

GTLREF2

GTLREF1

GTLREF0

STBP3

STBP2

STBP1

STBP0

STBN3

STBN2

STBN1

STBN0

BCLK1

BCLK0

IERR

MCERR

FERR

STPCLK

BINIT

INIT

RSP

DBSY

DRDY

TRDY

ADS

LOCK

BR0

BNR

HIT

HITM

BPRI

DEFER

TCK

TDI

TMS

TRST

TDO

THERMDA

THERMDC

THERMTRIP

PROCHOT

IGNNE

SMI

A20M

SLP

PWRGOOD

RESET

VSS_SENSE

DB#3

DB#2

DB#1

DB#0

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VCCIOPLL

VCCA

VSSA

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS

VSS VSS

VCCVIDPRG

BSEL0

BSEL1

COMP0

VCCVID

VSS

L69

4.7uH_SMD_30%

1 2

L71

4.7uH_SMD_30%

1 2

C317

47U/16V

C318

47U/16V

C316

220P

C330

1UF

C313

220P

C346

220P

C112

1UF

C349

220P

C376

0.1UF

C323

0.1UF

C113

0.1UF

PRDY#

PREQ#

ITP/TAP TERMINATION

CLOSE TO ITP PORT

CPU SIGNAL TERMINALION

CLOSE TO CPU

DBA#

20

mils

ITP/TAP TERMINATION

CLOSE TO CPU

NEAR U18

Sheet 3 of 35

Socket 478 & ITP

2 of 2