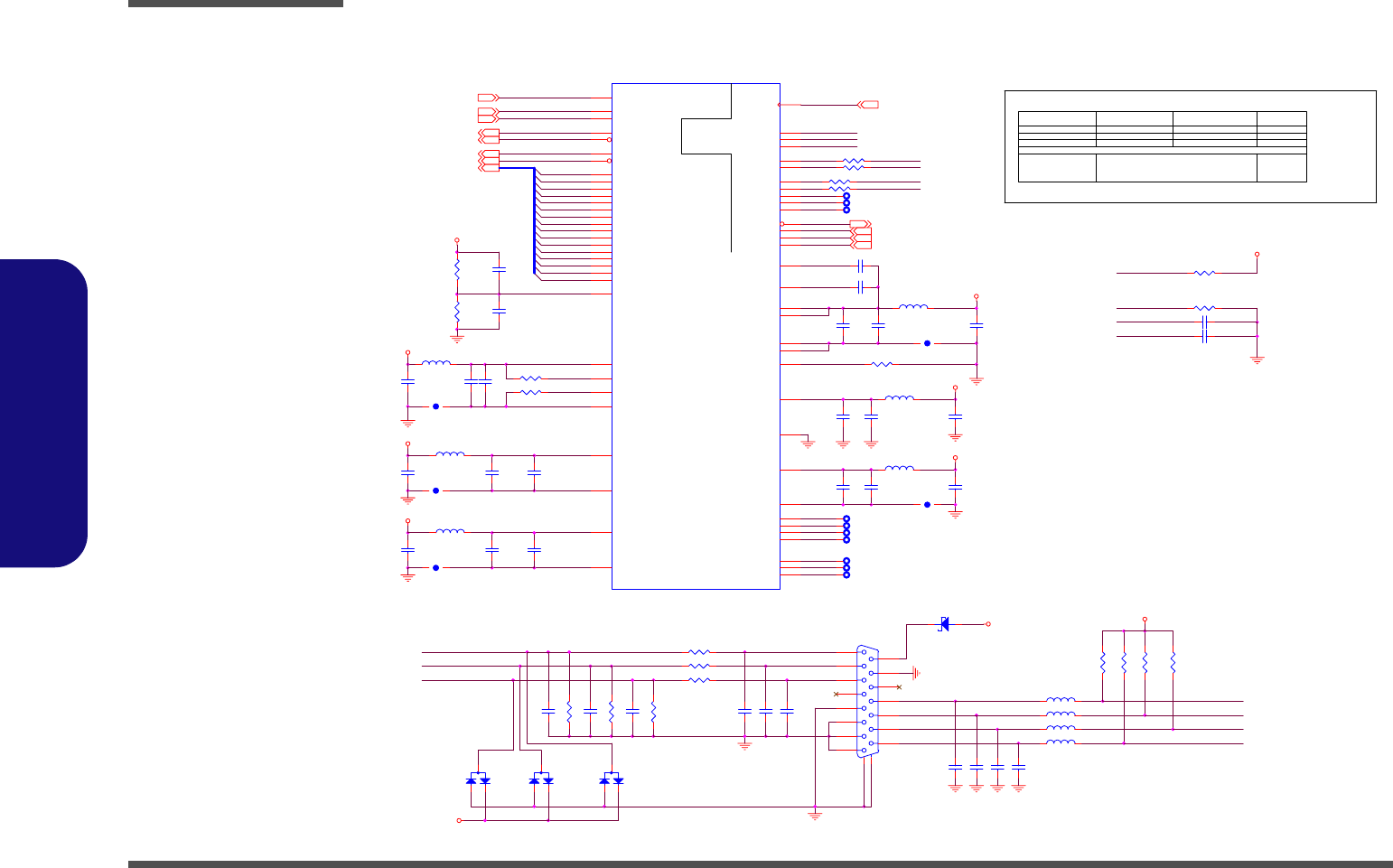

Schematic Diagrams

B - 8 M650 (& CRT Out) 3 of 4 (71-D4000-D04)

B.Schematic Diagrams

M650 (& CRT Out) 3 of 4

+3VS

+1.8VS

+1.8VS

+3VS

+3VS

+1.8VS

+3VS

+3VS

+5VS

+5VS

+5VS

INTA# [10,13]

PCIRST# [10,13,14,20,22,24]

REFCLK0 [4]

ZCLK0[4]

ZUREQ[13]

ZDREQ[13]

ZSTB0[13]

ZSTB#0[13]

ZSTB1[13]

ZSTB#1[13]

ZAD[0..15][13]

PWRGD [15,26,29]

AUXOK [15,24,28]

REFCLK0

ROUT

GOUT

BOUT

Z0801

HSYNC

Z0802

VSYNC

DDC1CLK

DDC1DATA

INTA#

Z1XAVDD

PWRGD

PCIRST#

AUXOK

CSYNC

RSYNC

LSYNC

RSYNC

PWRGD

AUXOK

ENTEST

ZAD10

ZSTB0

ZAD12

ZAD6

ZSTB#0

ZAD8

ZSTB#1

ZCMP_P

ZAD15

ZCLK0

ZAD14

ZAD9

ZAD1

ZAD0

ZUREQ

ZDREQ

ZAD7

ZVREF

ZAD2

ZAD13

ZAD11

ZAD5

ZAD3

ZSTB1

ZAD4

TRAP1

TRAP0

TMODE2

TMODE1

TMODE0

DLLEN#

ENTEST

ECLKAVSS

ECLKAVDD

DCLKAVDD

VVBWN

DACAVSS

VRSET

DACAVDD

VCOMP

Z1XAVSS

Z4XAVSS

Z4XAVDD

ZCMP_N

VDDZCMP

VSSZCMP

ZAD[0..15]

HS_10

GOUT

FBLU_10

FRED_10

FGRN_10

ROUT

MID1_10

VS_10

MID3_10 DDC1CLK

BOUT

HSYNC

VSYNC

DDC1DATA

N6

L22

FCM1608K121

1 2

N12

L52

FCM1608K121

1 2

L10

FCM1608K121

1 2

L9

FCM1608K121

1 2

N1

C413

0.01UF

C97

0.01UF

C399

0.1UF

C400

0.1UF

C94

0.01UF

C95

0.1UF

C87

10UF/10V

C428

0.1UF

C442 0.1UF

C271

0.1UF

C287

0.01UF

C21

0.01UF

C22

0.1UF

C13

10UF/10V

C265

10UF/10V

C20

0.1UF

C266

10UF/10V

C17

1UF

C18

0.1UF

C19

0.1UF

R230

33

R232

33

R47

150_1%

R46

150_1%

R49

56

R233

4.7K

R234 4.7K

C414

0.1UF

N15

L85

FCM1608K121

1 2

R16

130_1%

L24

FCM1608K121

1 2

C96

0.1UF

C93

10UF/10V

N7

C415

10UF/10V

R48

56

T

T

T

T

T

T

T

T

T

T

L6

FCM1608K121

1 2

L44

FCM1608K121

1 2

L45

FCM1608K121

1 2

R3 FCM1608K121

R4 FCM1608K121

R5 FCM1608K121

D2

DA204U

C

A

AC

C245

22P

C243

22P

C242

22P

D21

DA204U

C

A

AC

D3

DA204U

C

A

AC

C4

220P

C5

220P

C3

220P

C244

220P

L43

FCM1608K121

1 2

C7

22P

R200

75

C8

22P

R199

75

R201

75

C6

22P

D1 F01J2E

AC

R207

2.2K

R209

2.2K

R210

4.7K(R)

R208

4.7K(R)

R231 100

R229 100

BGA1C

SIS M650

C15

A12

B13

A13

F13

E13

D13

D12

B11

E12

A11

F12

E14

D14

F14

B12

C12

C13

C14

B15

A15

B14

A14

F10

E11

C11

F11

A10

D11

E10

Y3

W4

W6

V2

V1

W1

W2

V5

U4

U2

V6

U3

T4

R3

T5

T6

R2

R6

R1

R4

P4

N3

P5

P6

N1

N6

N2

N4

P1

P3

T3

T1

U6

U1

V3

VOSCI

ROUT

GOUT

BOUT

HSYNC

VSYNC

VGPIO0

VGPIO1

INT#A

CSYNC

RSYNC

LSYNC

VCOMP

VRSET

VVBWN

DACAVDD1

DACAVSS1

DACAVDD2

DACAVSS2

DCLKAVDD

DCLKAVSS

ECLKAVDD

ECLKAVSS

ENTEST

DLLEN#

TESTMODE0

TESTMODE1

TESTMODE2

TRAP1

TRAP0

PCIRST#

PWROK

AUXOK

Z4XAVDD

Z4XAVSS

Z1XAVDD

Z1XAVSS

VDDZCMP

ZCMP_N

ZCMP_P

VSSZCMP

ZVREF

ZAD0

ZAD1

ZAD2

ZAD3

ZAD4

ZAD5

ZAD6

ZAD7

ZAD8

ZAD9

ZAD10

ZAD11

ZAD12

ZAD13

ZAD14

ZAD15

ZSTB1

ZSTB#1

ZSTB0

ZSTB#0

ZUREQ

ZDREQ

ZCLK

VJVGA1

CEN/VGA DSUB

8

7

6

5

4

3

2

1

9

10

11

12

13

14

15

16

17

M650-3

VGA

HyperZip

DLLEN#

DRAM_SEL

TRAP0

TRAP1

SDR

LSYNC

CSYNC

RSYNC

1(DDR)

(30~50K Ohm)Default

DDR

0

1

0

embedded pull-low

0

0 yes

disable PLL

yes

1

NB debug mode

0

yes

0

normal

NOTE: This page is for universal PCB design( suitable for both 645 or 650)

NB Hardware Trap Table

enable panel link

enable VGA interface

enable PLL

TV selection, NTSC/PAL(0/1)

enable VB

35.4mA

6.49mA

7.92mA

84.8mA

7.57mA

18.07mA

20MIL

10MIL

10MIL

10MIL

20MIL

10MIL

Sheet 7 of 35

M650 & CRT Out

3 of 4